Clock Description

MPC5606S Microcontroller Reference Manual, Rev. 7

Freescale Semiconductor 221

8.9.6 Functional description

8.9.6.1 Normal mode

In Normal mode, the PLL inputs are driven by the CR (see Section 8.9.5.1, Control Register (CR)). This

means that when the PLL is in lock state, the PLL output clock (PHI) is derived from the reference clock

(CLKIN) through Equation 8-1:

Eqn. 8-1

where the value of IDF, LDF, and ODF are set in CR and can be derived from Table 8-22, Table 8-23, and

Table 8-24.

8.9.6.2 Progressive clock switching

Progressive clock switching allows switching the system clock to PLL output clock by stepping through

different division factors. This means that the current consumption gradually increases, so the voltage

regulator has a better response.

This feature can be enabled by programming the en_pll_sw bit in CR. Then, when the input pin pll_select

goes high, the output clock ck_pll_div will progressively increase its frequency as described in

Table 8-26

and Figure 8-26.

16

FM_EN

Frequency Modulation Enable

The FM_EN enables the frequency modulation.

0 = Frequency Modulation disabled

1= Frequency Modulation enabled

17–31

INC_STEP

Increment step

The INC_STEP field is the binary equivalent of the value incstep derived from the following

formula:

where:

md: represents the peak modulation depth in percentage (Center spread — pk-pk = ±md,

Downspread — pk-pk = -2 × md)

MDF: represents the nominal value of loop divider (NDIV in PLL Control Register)

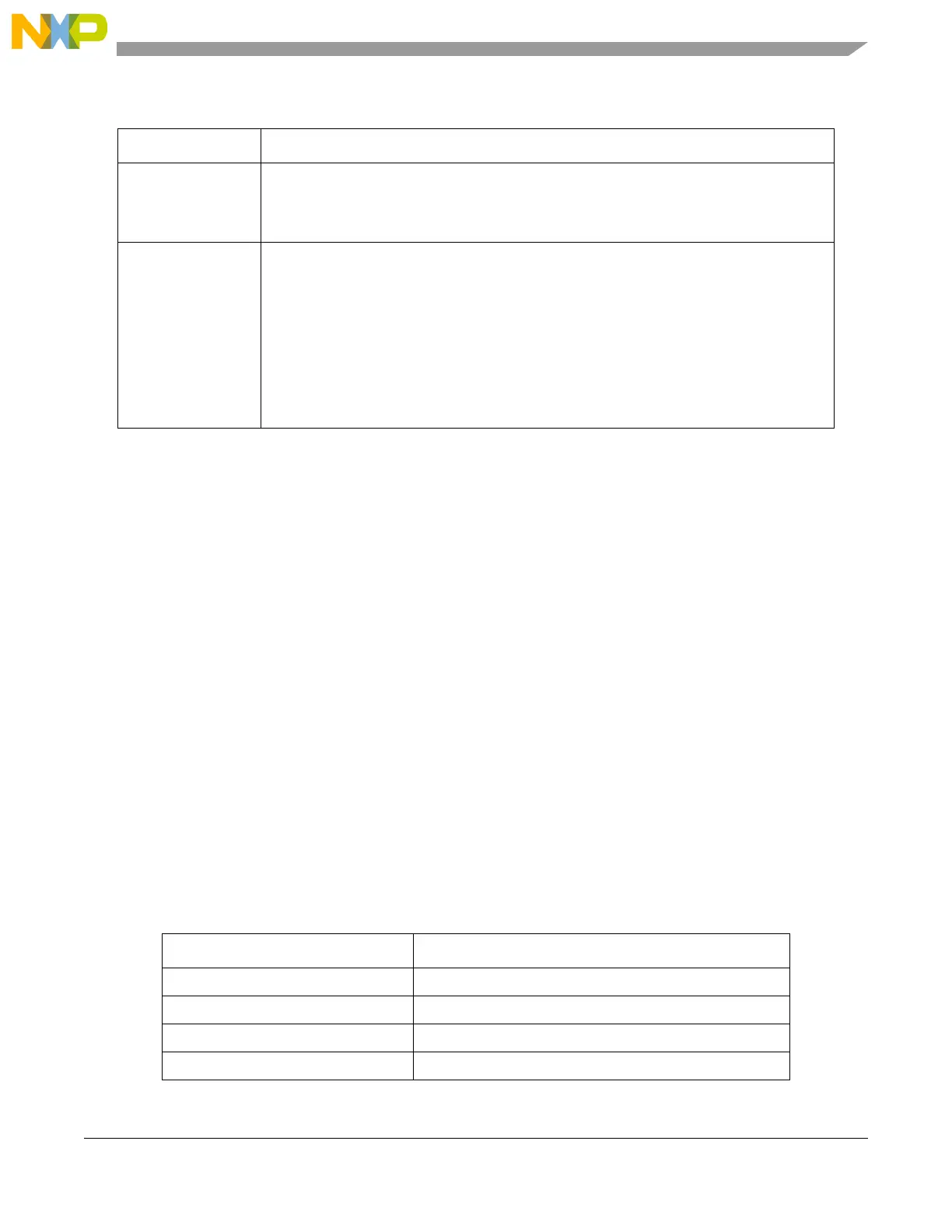

Table 8-26. Progressive clock switching on pll_select rising edge

Number of PLL output clock cycles ck_pll_frequency (PLL output clock frequency)

8 (ck_pll_out frequency)/8

16 (ck_pll_out frequency)/4

32 (ck_pll_out frequency)/2

onward (ck_pll_out frequency)

Table 8-25. MR field descriptions (continued)

Field Description

incstep round

2

15

1–md MDF

100 5 MODPERIOD

---------------------------------------------------------------

=

phi

clkin LDF

IDF ODF

-----------------------------

=

Loading...

Loading...