Quad Serial Peripheral Interface (QuadSPI)

MPC5606S Microcontroller Reference Manual, Rev. 7

1006 Freescale Semiconductor

30.4.3.3 Transfer Count Register (QSPI_TCR)

The QSPI_TCR contains a counter that indicates the number of SPI transfers made. The transfer counter

is intended to assist in queue management.

SMPL_PT SMPL_PT — Only applicable if QMODE is cleared. Sample Point. SMPL_PT allows the host

software to select when the QuadSPI Master samples SI in Modified Transfer Format. The table

below lists the various delayed sample points.

00 0 system clock cycles

01 1 system clock cycle

10 2 system clock cycles

11 Reserved

QMODE QMODE — QuadSPI Mode: When this bit is cleared the QuadSPI block is in SPI Master or SPI Slave

mode. When this bit is set the QuadSPI block is in Serial Flash mode.

0 Module is in SPI Master or SPI Slave mode

1 Module is in SFM mode

VMID VMID — Vendor Model ID. Only applicable if QMODE is set.

0000 Reserved

0001 Winbond

othersReserved

HALT Halt. Only applicable if QMODE is cleared. The HALT bit provides a mechanism by software to start

and stop QuadSPI transfers. See Section 30.5.2.1, Start and Stop of SPI Transfers, for details about

the operation of this bit.

0 Start transfers

1 Stop transfers

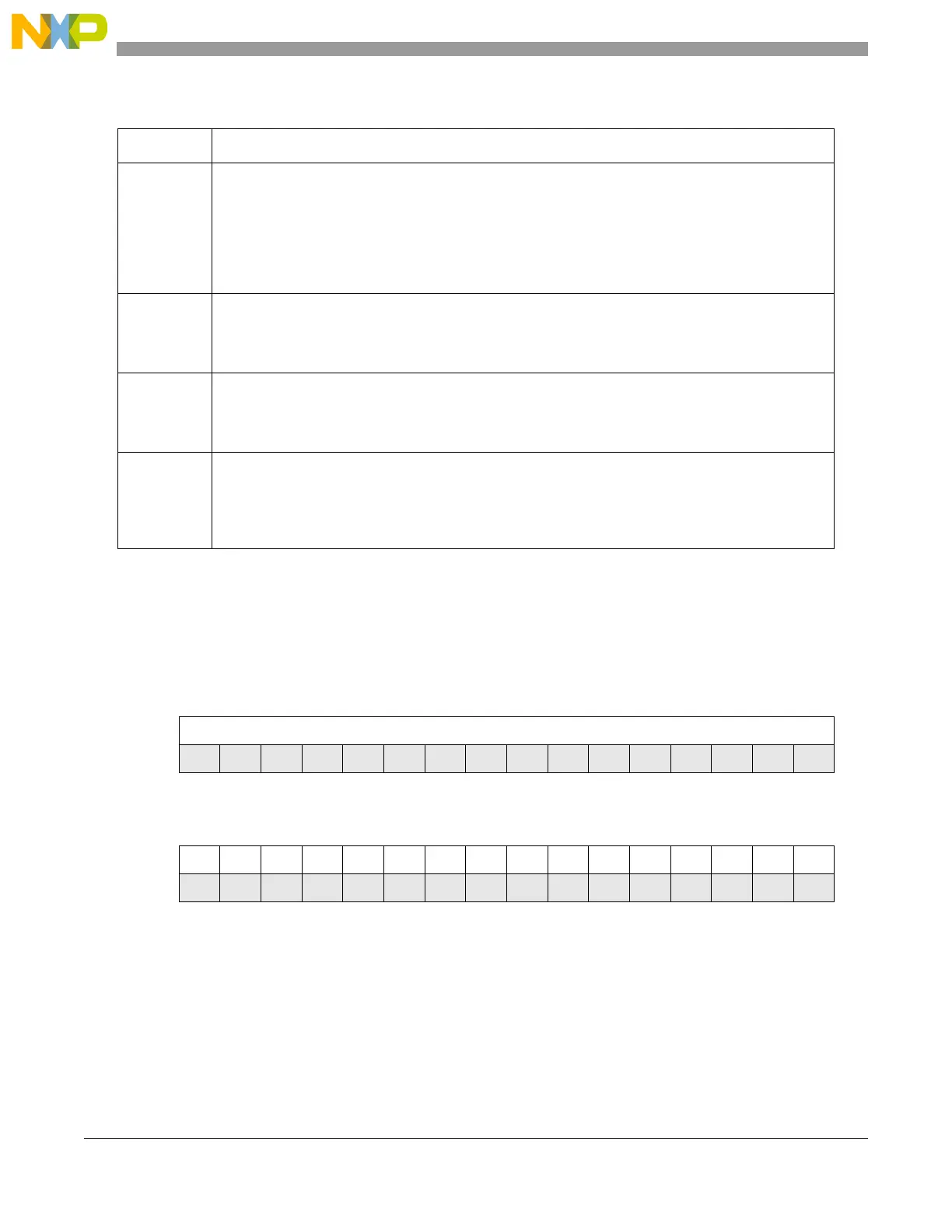

Address: QSPI_BASE + 0x008

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R SPI_TCNT

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Figure 30-3. Transfer Count Register (QSPI_TCR)

Table 30-9. QSPI_MCR field descriptions (continued)

Field Description

Loading...

Loading...