LIN Controller (LINFlex)

MPC5606S Microcontroller Reference Manual, Rev. 7

858 Freescale Semiconductor

23.7.2.17 Identifier filter enable register (IFER)

This register is not implemented on LINFlex_1.

Table 23-22. BDRM field descriptions

Field Description

DATA7[0:7]

0:7

Data Byte 7

Data byte 7 of the data field.

DATA6[0:7]

8:15

Data Byte 6

Data byte 6 of the data field.

DATA5[0:7]

16:23

Data Byte 5

Data byte 5 of the data field.

DATA4[0:7]

24:31

Data Byte 4

Data byte 4 of the data field.

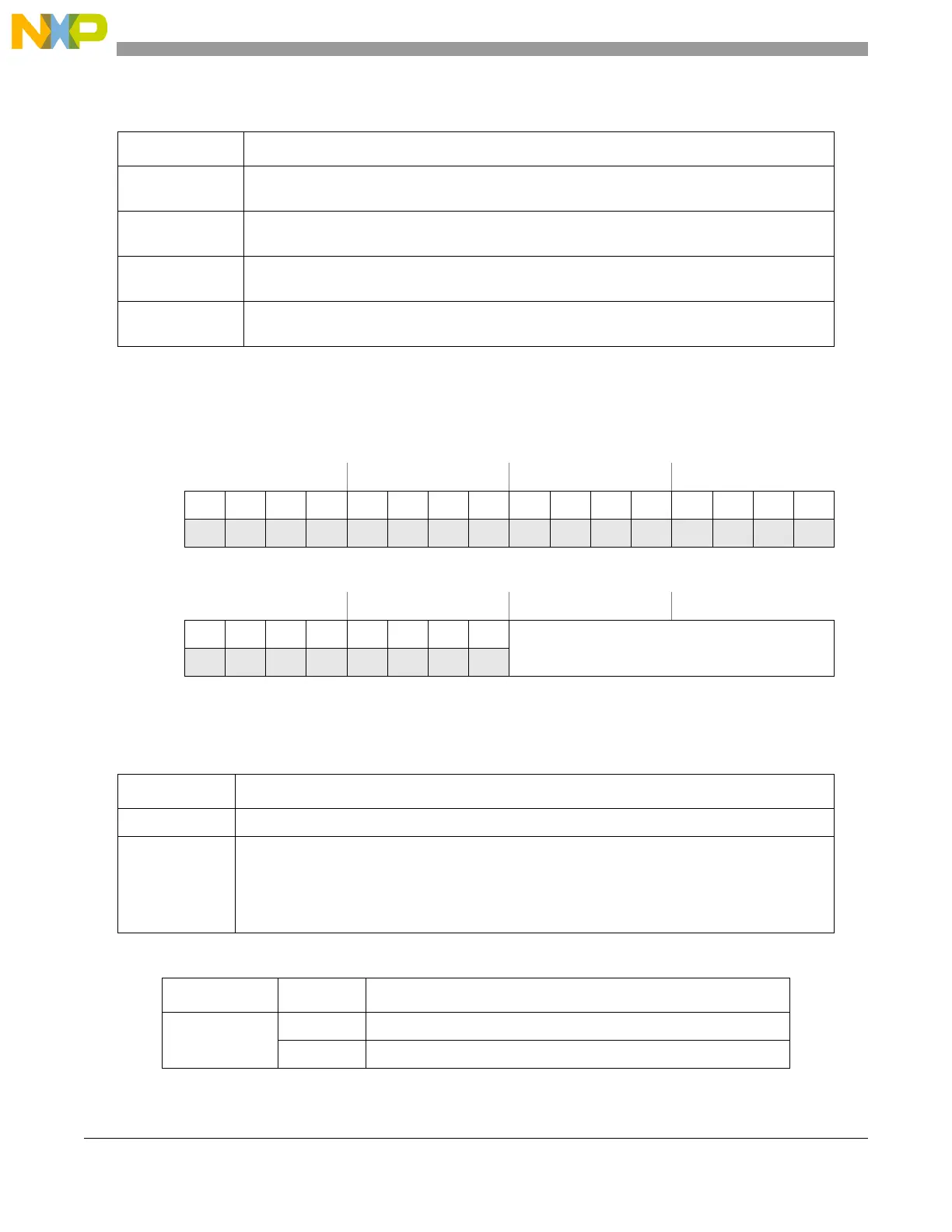

Address: Base + 0x0040 Access: User read/write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0 0 0

FACT[0:7]

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Figure 23-23. Identifier filter enable register (IFER)

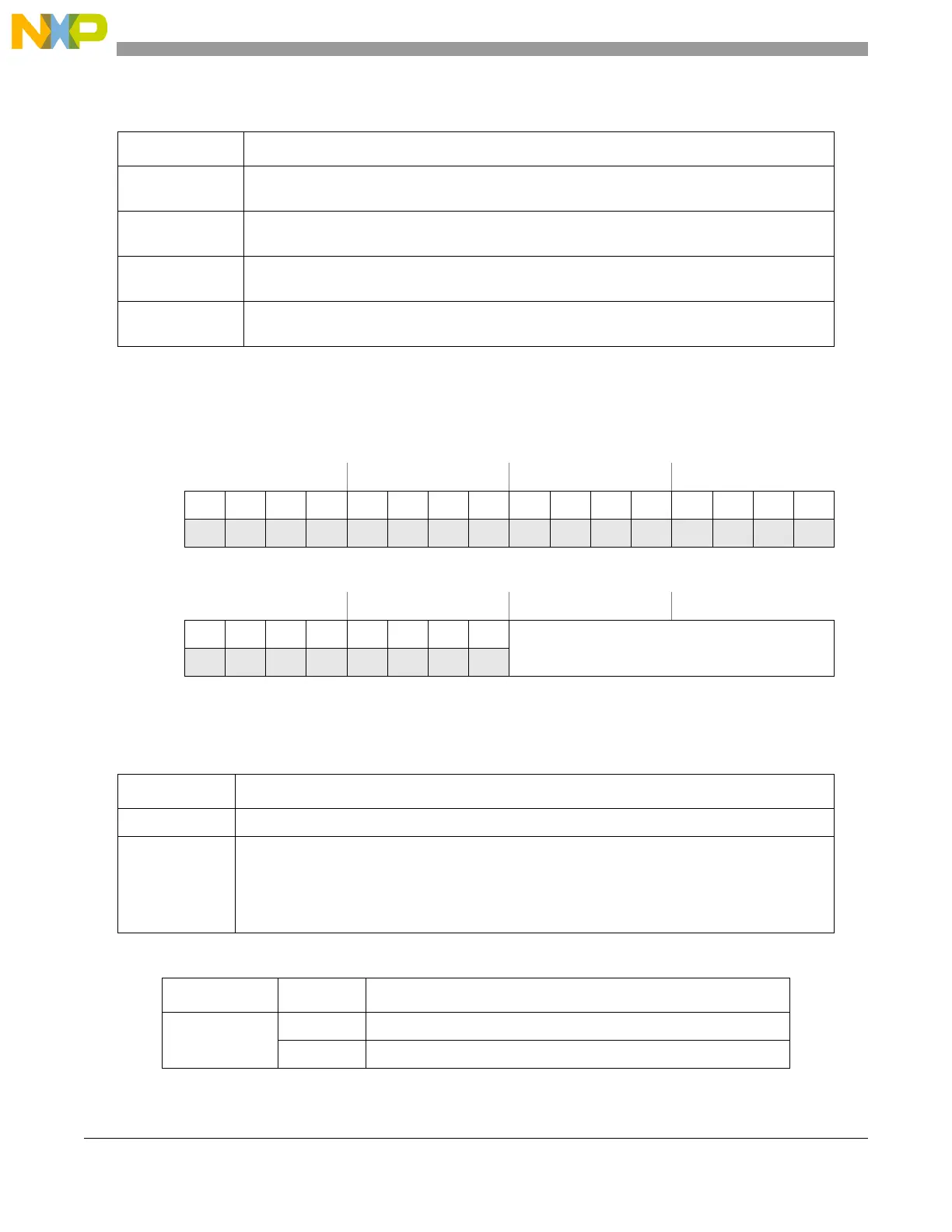

Table 23-23. IFER field descriptions

Field Description

0:23 Reserved

FACT[0:7]

24:31

Filter activation

0 Filters 2n and 2n + 1 are activated.

1 Filters 2n and 2n + 1 are deactivated.

(Refer to Table 23-24.)

These bits can be set/cleared in Initialization mode only.

Table 23-24. IFER[FACT] configuration

Bit Value Result

FACT[0] 0 Filters 0 and 1 are deactivated.

1 Filters 0 and 1 are activated.

Loading...

Loading...