Deserial Serial Peripheral Interface (DSPI)

MPC5606S Microcontroller Reference Manual, Rev. 7

Freescale Semiconductor 299

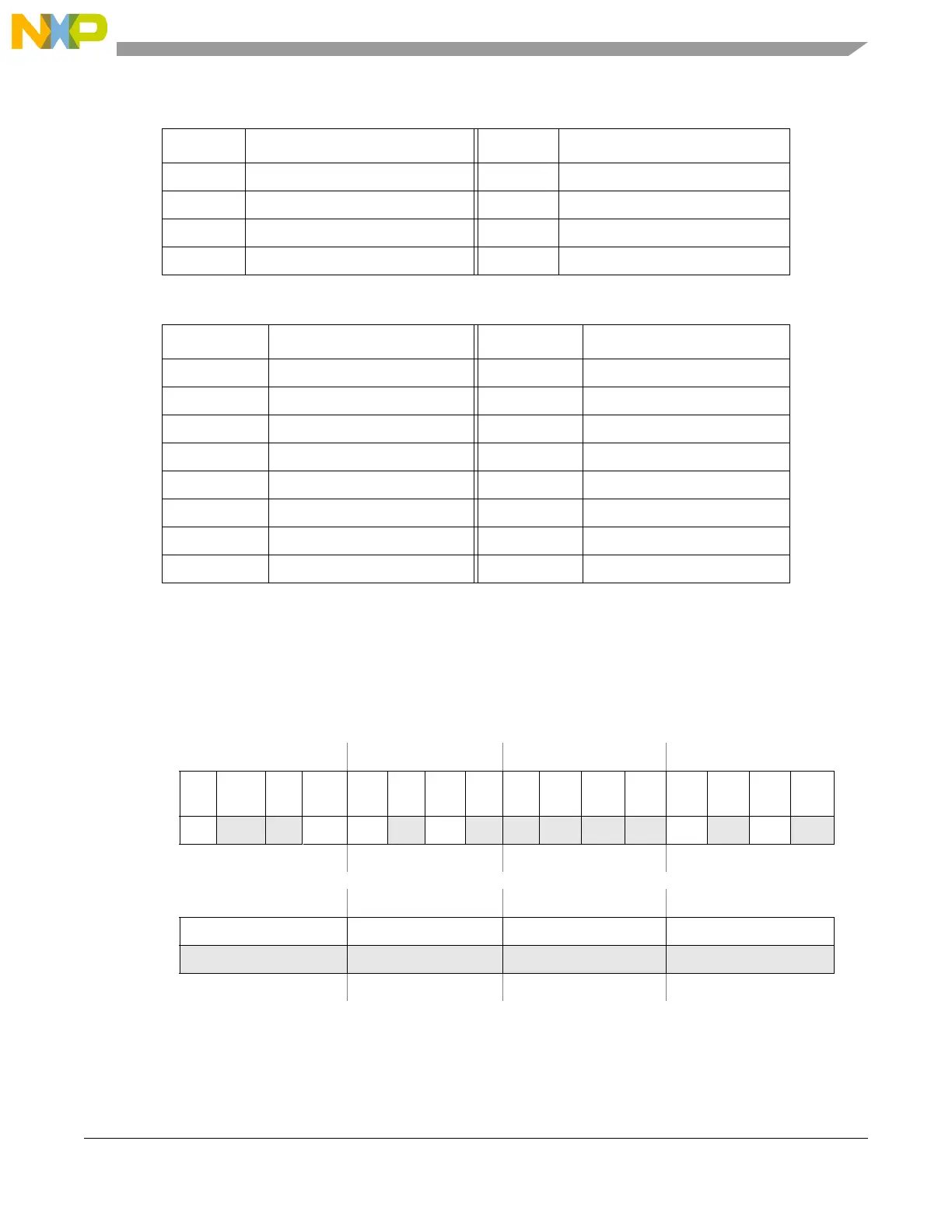

11.7.2.4 DSPI Status Register (DSPIx_SR)

The DSPIx_SR contains status and flag bits. The bits are set by the hardware and reflect the status of the

DSPI and indicate the occurrence of events that can generate interrupt or DMA requests. Software can

clear flag bits in the DSPIx_SR by writing a 1 to clear (w1c). Writing a 0 to a flag bit has no effect.

0100 32 1100 8192

0101 64 1101 16384

0110 128 1110 32768

0111 256 1111 65536

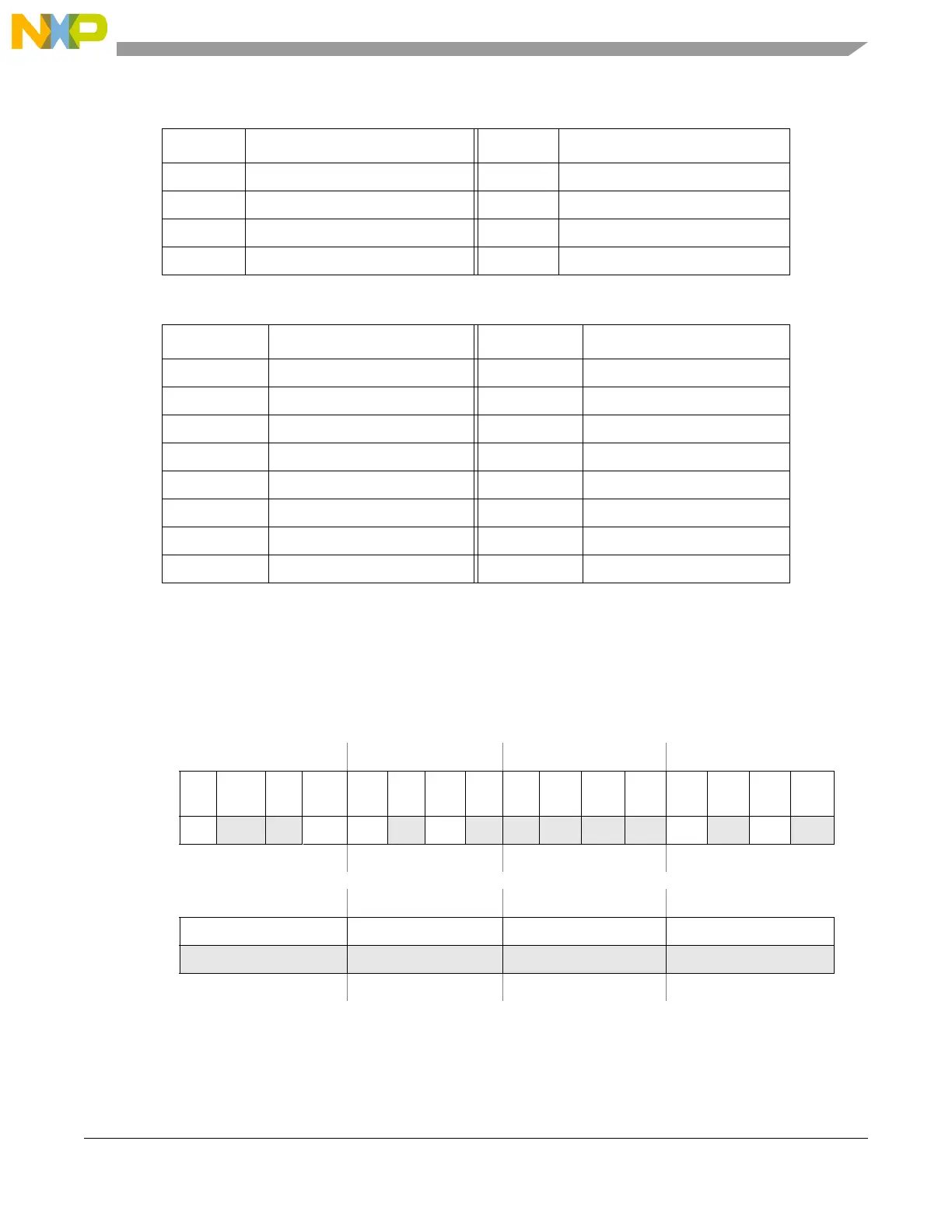

Table 11-11. DSPI baud rate scaler

BR Baud rate scaler value BR Baud rate scaler value

0000 2 1000 256

0001 4 1001 512

0010 6 1010 1024

0011 8 1011 2048

0100 16 1100 4096

0101 32 1101 8192

0110 64 1110 16384

0111 128 1111 32768

Address: Base + 0x002C Access: User read/write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

TCF

TXRX

S

0

EOQ

F

TFU

F

0 TFFF 0 0 0 0 0

RFO

F

0

RFD

F

0

W w1c w1c w1c w1c w1c w1c

Reset 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R TXCTR TXNXTPTR RXCTR POPNXTPTR

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DSPI Status Register (DSPIx_SR)

Table 11-10. DSPI delay after transfer scaler (continued) (continued)

DT Delay after transfer scaler value DT Delay after transfer scaler value

Loading...

Loading...