Quad Serial Peripheral Interface (QuadSPI)

MPC5606S Microcontroller Reference Manual, Rev. 7

Freescale Semiconductor 1033

Both SPI modes and the SFM mode share transfer protocol and timing properties so they are described

independently of the mode in Section 30.5.2.8, SPI Transfer Formats. The transfer rate and delay settings

are described in Section 30.5.2.7, Baud Rate and Clock Delay Generation.

The QSPI_CTAR0–QSPI_CTAR7 registers hold clock and transfer attributes. In the SPI Master mode the

user can select which CTAR to use on a frame by frame basis by setting a field in the SPI Command. See

Section 30.4.3.4, Clock and Transfer Attributes Registers 0 – 1 (QSPI_CTAR0 – QSPI_CTAR1), for

information on the fields of the QSPI_CTAR registers.

See Section 30.5.4, Power saving features, for information on the power-saving features of the QuadSPI.

30.5.2.1 Start and Stop of SPI Transfers

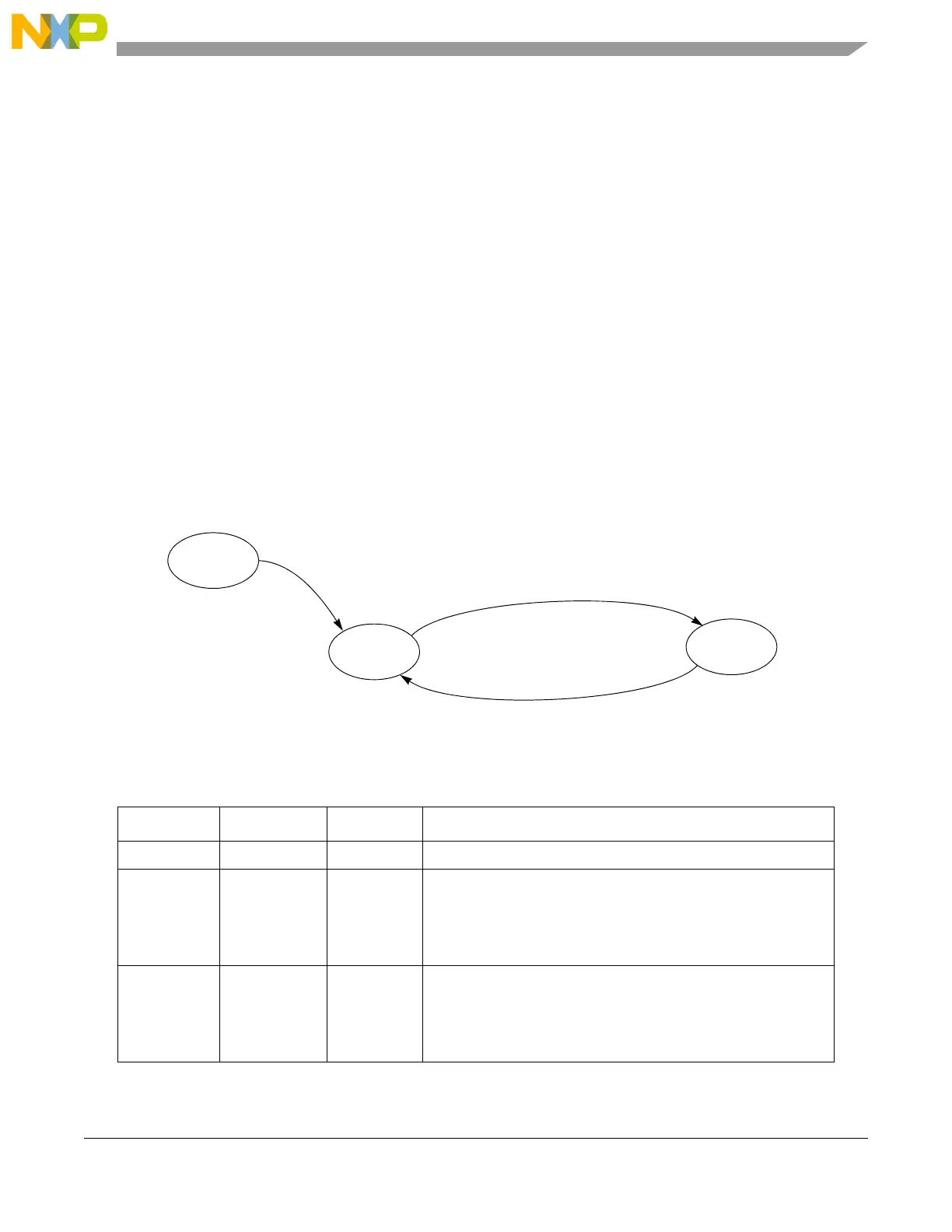

The QuadSPI in SPI Master or Slave mode has two operating states; Stopped and Running. The default

state is Stopped. In the Stopped state no serial transfers are initiated in Master mode and no transfers are

responded to in Slave mode. The Stopped state is also a safe state for writing the various configuration

registers of the QuadSPI without causing undetermined results. The TXRXS bit in the QSPI_SPISR is

negated in this state. In the Running state serial transfers take place. The TXRXS bit in the QSPI_SPISR

is asserted in the Running state. Figure 30-24 shows a state diagram of the start and stop mechanism. The

transitions are described in Table 30-37.

Figure 30-24. QuadSPI Start and Stop State Diagram

Table 30-37. State Transitions for Start and Stop of QuadSPI Transfers

Transition # Current State Next State Description

0 RESET Stopped Generic power-on reset transition

1 Stopped Running The QuadSPI is started (SPI state transitions to Running) when all

of the following conditions are true:

• EOQF bit is clear

• HALT bit is clear

• ipg_debug is clear OR FRZ is clear

2 Running Stopped The QuadSPI stops (transitions from Running to Stopped) after

the current frame for any one of the following conditions:

• EOQF bit is set

• HALT bit is set

• ipg_debug is set AND FRZ is set

RESET

Stopped

Running

Power-on

TXRXS=0

TXRXS=1

reset

2

1

0

Loading...

Loading...