Safety

MPC5606S Microcontroller Reference Manual, Rev. 7

122 Freescale Semiconductor

4.2.5.1 Memory map

The SWT memory map is shown in Table 4-6.

4.2.5.2 SWT Control Register (SWT_CR)

The SWT_CR contains fields for configuring and controlling the SWT. This register is read only if either

the SWT_CR[HLK] or SWT_CR[SLK] bits are set.

The SWT_CR reset value is 0x8000_011A or 0x8000_011B, corresponding to MAP0 = 1 (only CPU

access allowed), RIA

= 1 (reset on invalid SWT access), SLK = 1 (soft lock), CSL = 1 (IRC clock source

for counter), FRZ

= 1 (freeze available while debugging), WEN = 0 or 1 (copied from configuration bit

NVUSR0[WATCHDOG_EN]).

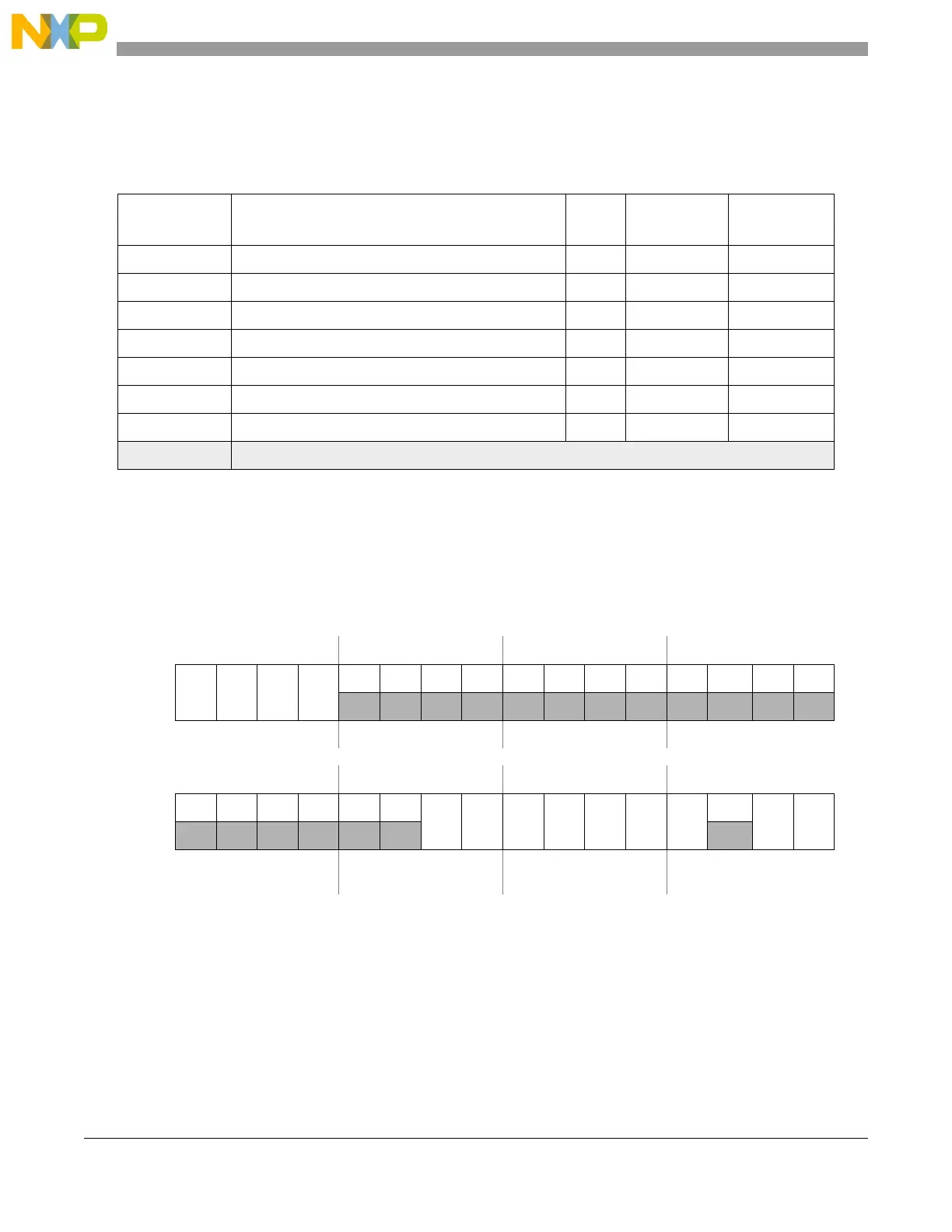

Table 4-6. SWT memory map

Offset from

SWT_BASE

Register

Access

1

1

In this column, R/W = Read/Write, R = Read-only, and W = Write-only.

Reset Value Location

0x0000 SWT Control Register (SWT_CR) R/W 0xFF00_011B on page 122

0x0004 SWT Interrupt Register (SWT_IR) R/W 0x0000_0000 on page 123

0x0008 SWT Timeout Register (SWT_TO) R/W 0x0003_FDE0 on page 124

0x000C SWT Window Register (SWT_WN) R/W 0x0000_0000 on page 125

0x0010 SWT Service Register (SWT_SR) W 0x0000_0000 on page 125

0x0014 SWT Counter Output Register (SWT_CO) R 0x0000_0000 on page 126

0x0018 SWT Service Key Register (SWT_SK) W 0x0000_0000 on page 126

0x001C–0x3FFF Reserved

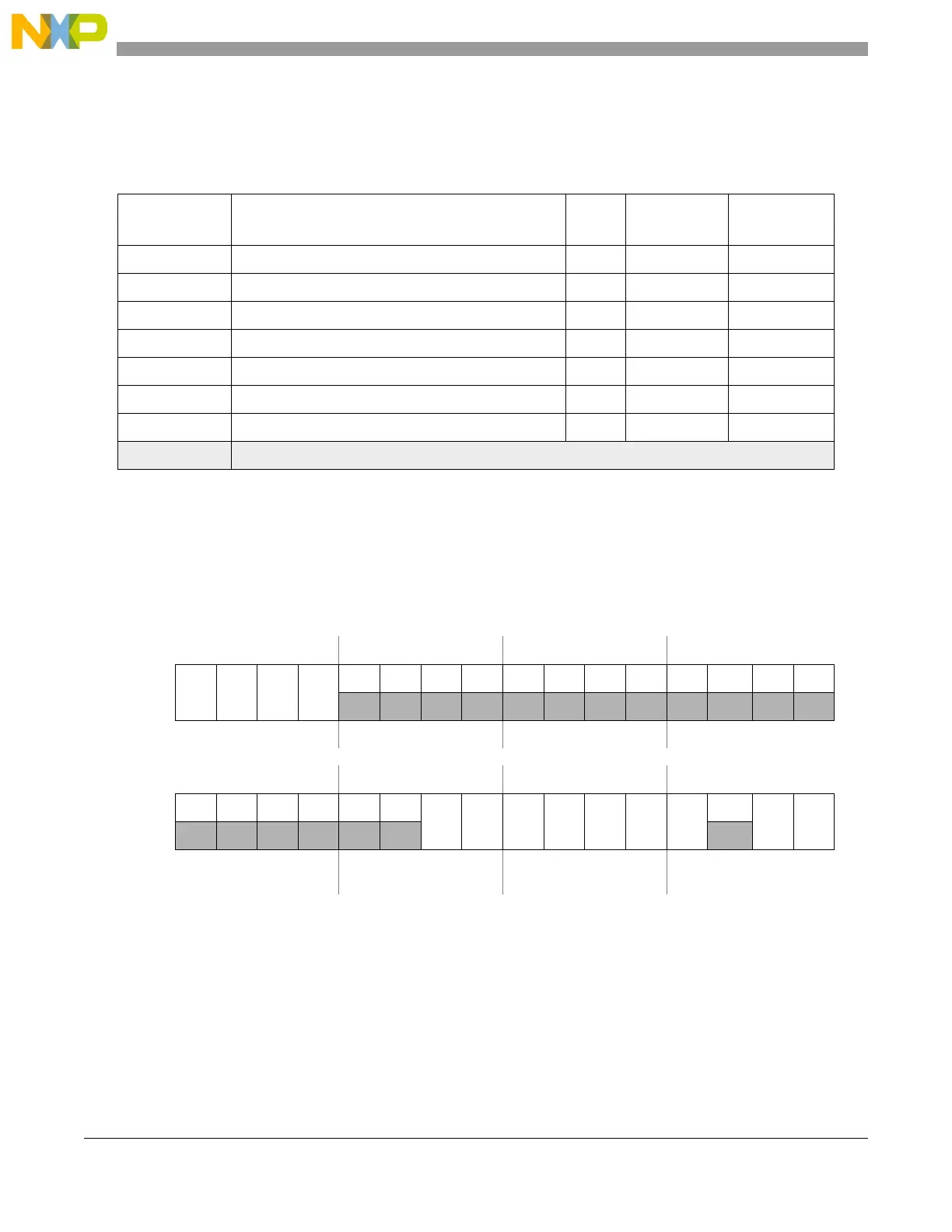

Offset 0x0000 Access: Read/Write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

MAP

0

MAP

1

MAP

2

MAP

3

0 0 0 0 0 0 0 0 0 0 0 0

W

Reset 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0

KEY RIA WND ITR HLK SLK CSL

0

FRZ WEN

W

Reset

0 0 0 0 0 0 0 1 0 0 0 1 1 0 1

See

note

Note: SWT_CR[WEN] value is copied from configuration bit NVUSR0[WATCHDOG_EN] during reset

Figure 4-12. SWT Control Register (SWT_CR)

Loading...

Loading...