MPC5606S Microcontroller Reference Manual, Rev. 7

40 Freescale Semiconductor

References

In addition to this reference manual, the following documents provide additional information on the

operation of the MPC5606S:

• IEEE-ISTO 5001-2003 Standard for a Global Embedded Processor Interface (Nexus)

• IEEE 1149.1-2001 standard—IEEE Standard Test Access Port and Boundary-Scan Architecture

• Power Architecture (http://www.freescale.com/files/32bit/doc/user_guide/BOOK_EUM.pdf)

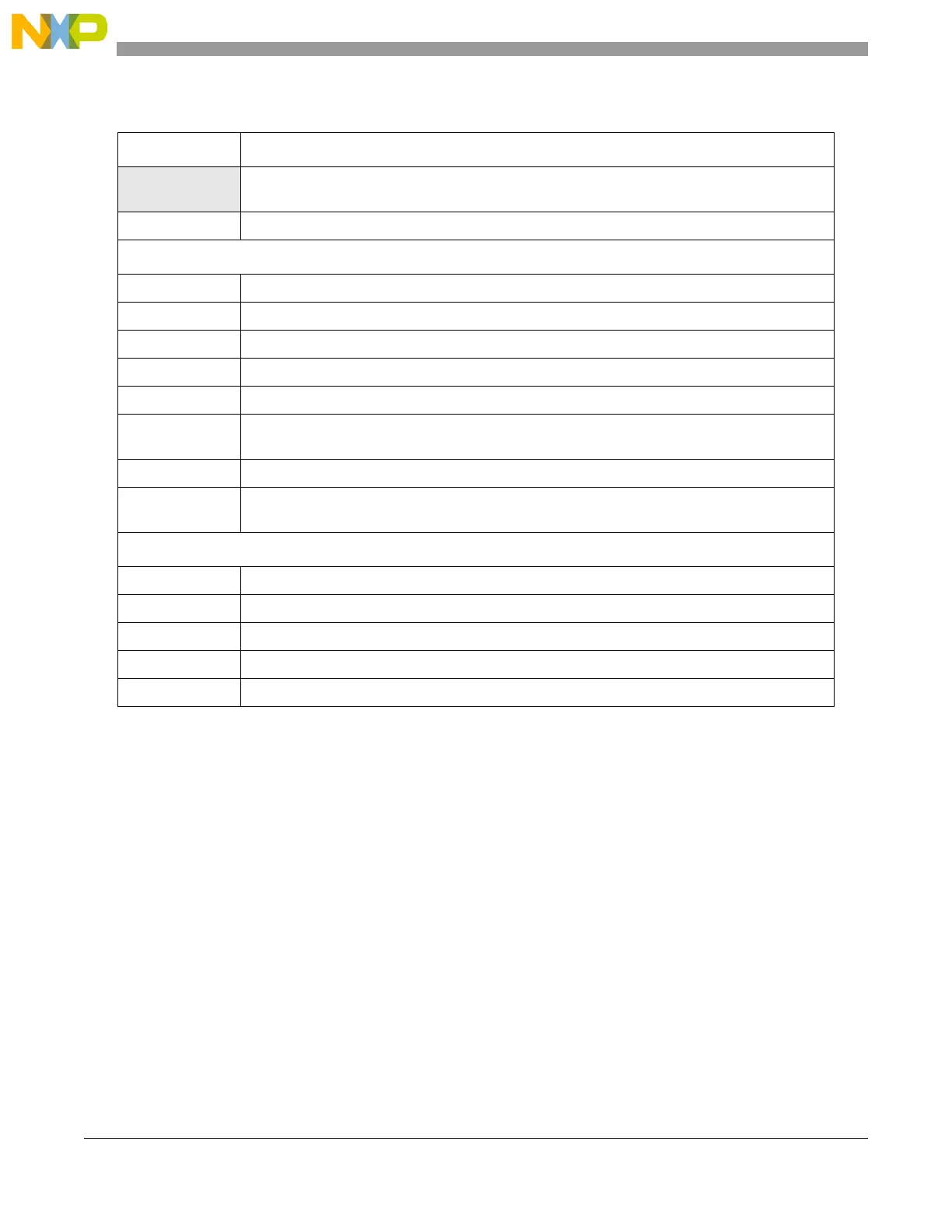

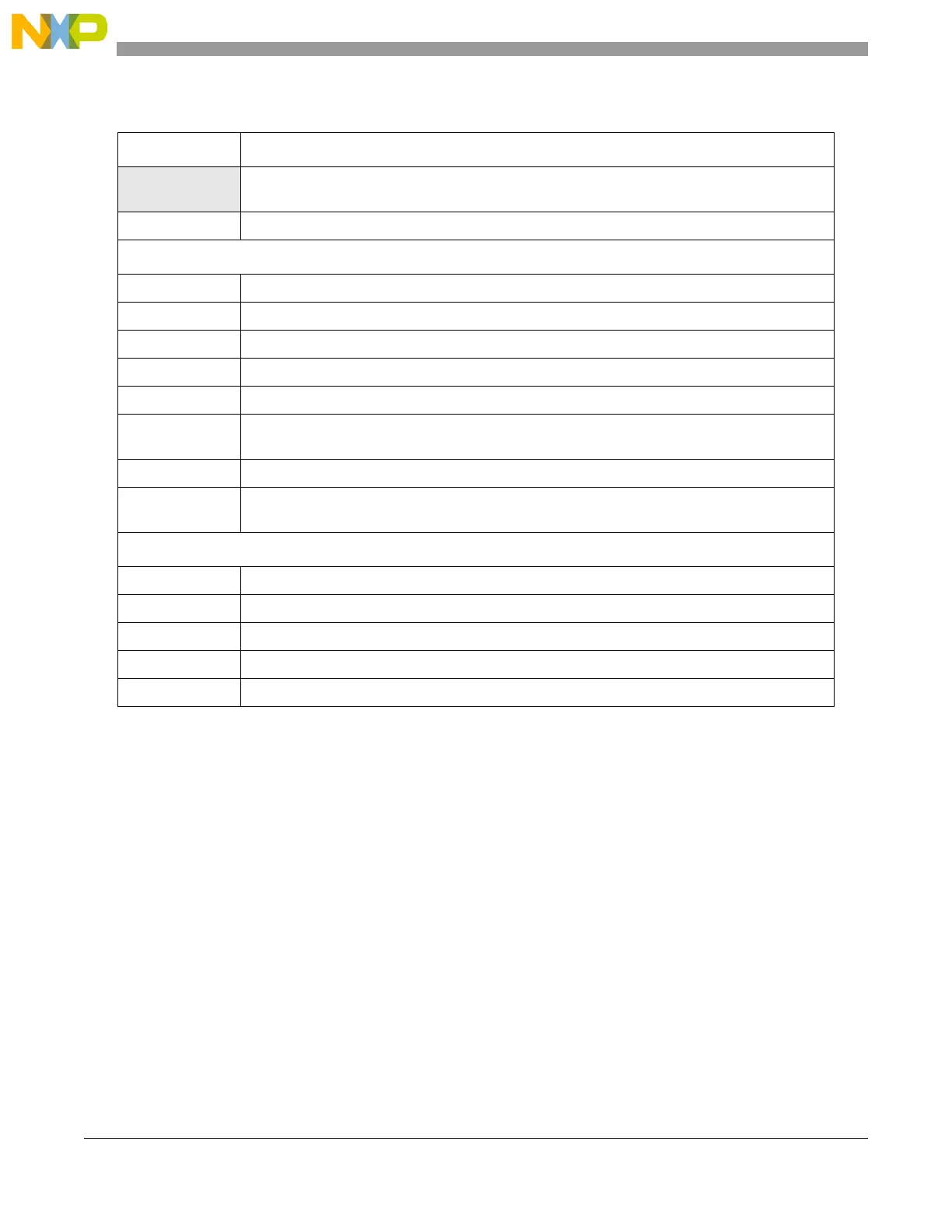

Table 0-1. Register conventions

Convention Description

Depending on its placement in the read or write row, indicates that the bit is not readable or not

writable

FIELDNAME Identifies the field. Its presence in the read or write row indicates that it can be read or written.

Register field types

R Read only. Writing this bit has no effect

W Write only

R/W Standard read/write bit. Only software can change the bit’s value (other than a hardware reset).

rwm A read/write bit that can be modified by hardware in some fashion other than by a reset

w1c Write one to clear. A status bit that can be read, and is cleared by writing a one.

Self-clearing bit Writing a one has some effect on the module, but it always reads as zero. (Previously designated

slfclr)

S Set: Pattern on the data bus is ORed with and written into the register.

C Clear: Pattern on the data bus is a mask. If a bit on the mask is set, then the corresponding

register bit is cleared.

Reset values

0 Resets to zero

1 Resets to one

— Undefined at reset

u Unaffected by reset

[signal_name] Reset value is determined by polarity of indicated signal.

Loading...

Loading...