Quad Serial Peripheral Interface (QuadSPI)

MPC5606S Microcontroller Reference Manual, Rev. 7

Freescale Semiconductor 1069

Depending from the actual delay and the serial flash clock frequency the appropriate sampling point can

be chosen. The following remarks should be considered when selecting the appropriate setting:

• Theoretically there should be 2 settings possible to capture the correct data since the serial flash

output is valid for 1 clock cycle, disregarding rise and fall times and timing uncertainties.

• Depending from the timing uncertainties it may turn out in actual applications that only one

possible sample positions remains. This is subject to careful consideration depending from the

actual implementation.

• The delay t

Del,total

is an absolute size to shift the point in time when the serial flash date get valid

at the QuadSPI input.

• For decreasing frequency of the serial flash clock the distance between the edges increases. So for

large differences in the frequency the required setting may change.

• For commands running at half of the regular serial flash clock (QSPI_SMPR[HSENA] bit set) the

sampling point must be figured separately to allow for the compensation of the absolute shift in

time w.r.t. the sample-relative setting in the QSPI_SPMPR register.

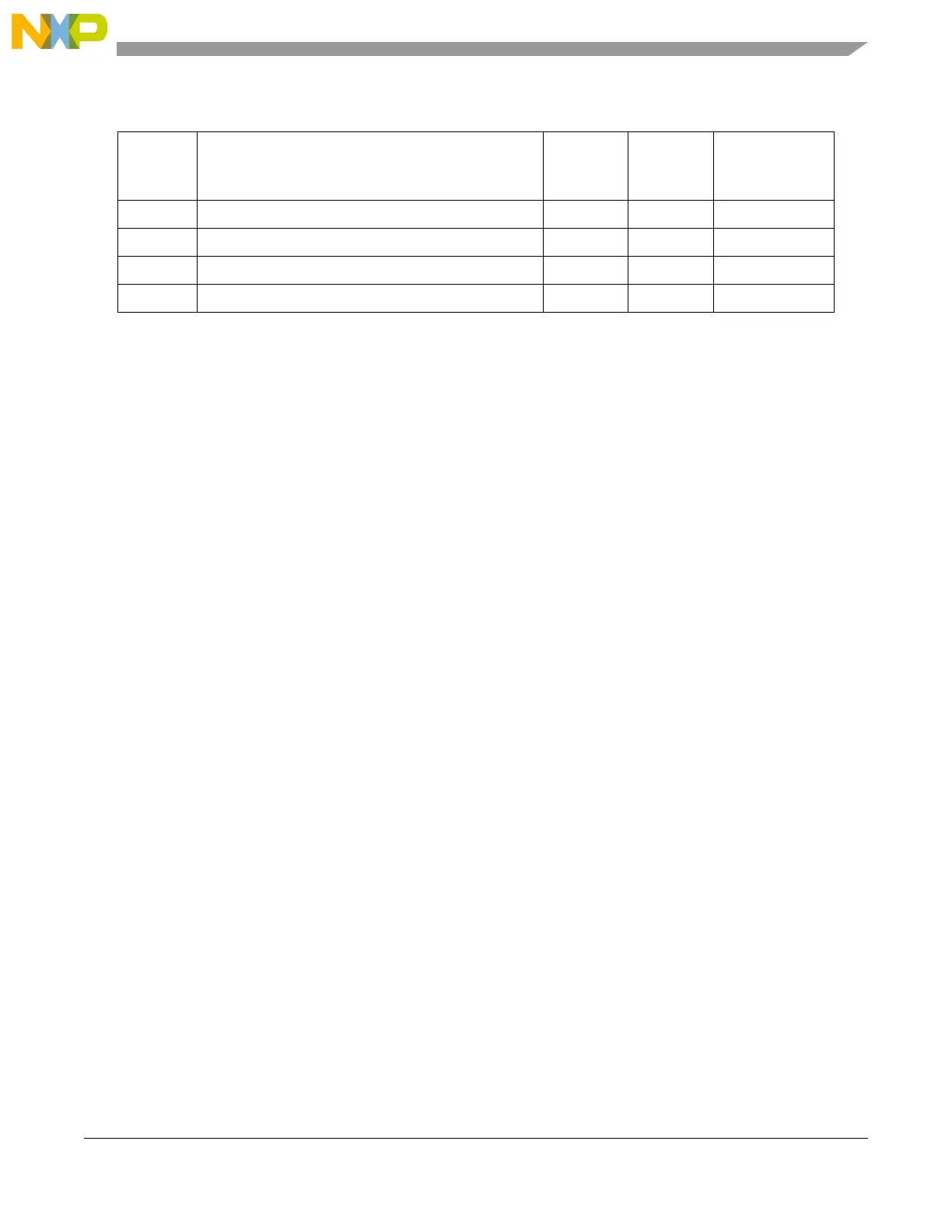

Table 30-54. Sampling Configuration

Sampling

Point

Description

Delay

[FSDLY]

[HSDLY]

Phase

[FSPHS]

[HSPHS]

QSPI_SMPR for

Full Speed

Setting

1

1

‘x’ is not considered here

N/1 sampling with non-inverted clock, 1 sample delay 0 0 0x0000000x

I/1 sampling with inverted clock, 1 sample delay 0 1 0x0000002x

N/2 sampling with non-inverted clock, 2 samples delay 1 0 0x0000004x

I/2 sampling with inverted clock, 2 samples delay 1 1 0x0000006x

Loading...

Loading...