Analog-to-Digital Converter (ADC)

MPC5606S Microcontroller Reference Manual, Rev. 7

136 Freescale Semiconductor

The total evaluation phase duration is:

INPCMP must be greater than or equal to 1 and INPLATCH must be less than INPCMP (hardware

requirements).

The total conversion duration is (not including external multiplexing):

The timings refer to the unit T

ck

, where f

ck

= (1/2 x ADC peripheral set clock). The maximum clock

frequency is specified in Table 5-2.

Table 5-3 lists the possible combinations by configuring the AD_clk at 60 MHz.

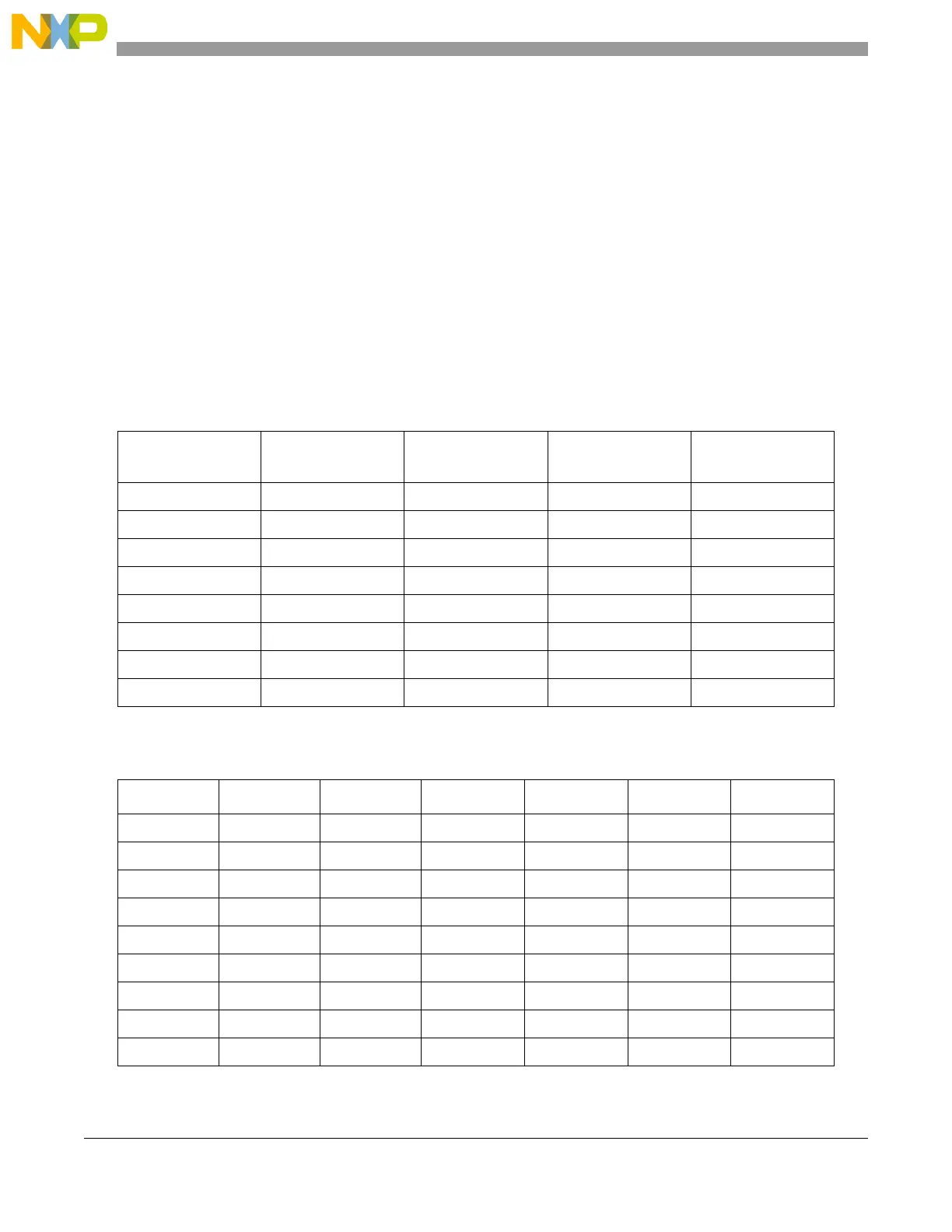

Table 5-2. Max AD_clk frequency and related configuration settings

INPLATCH INPCMP INPSAMP

AD_clk f

max

(MHz)

T

sample

min.

(ns)

0 0x1 0x3 20 125

0 0x1 0x4 20 + 4% 168

1 0x2 0x4 20 + 4% 168

1 0x2 0x5 20 + 4% 135

1 0x3 0x7 32 + 4% 132

1 0x3 0x7 40 + 4% 128

1 0x3 0x8 50 + 4% 134

1 0x3 0x9 60 + 4% 128

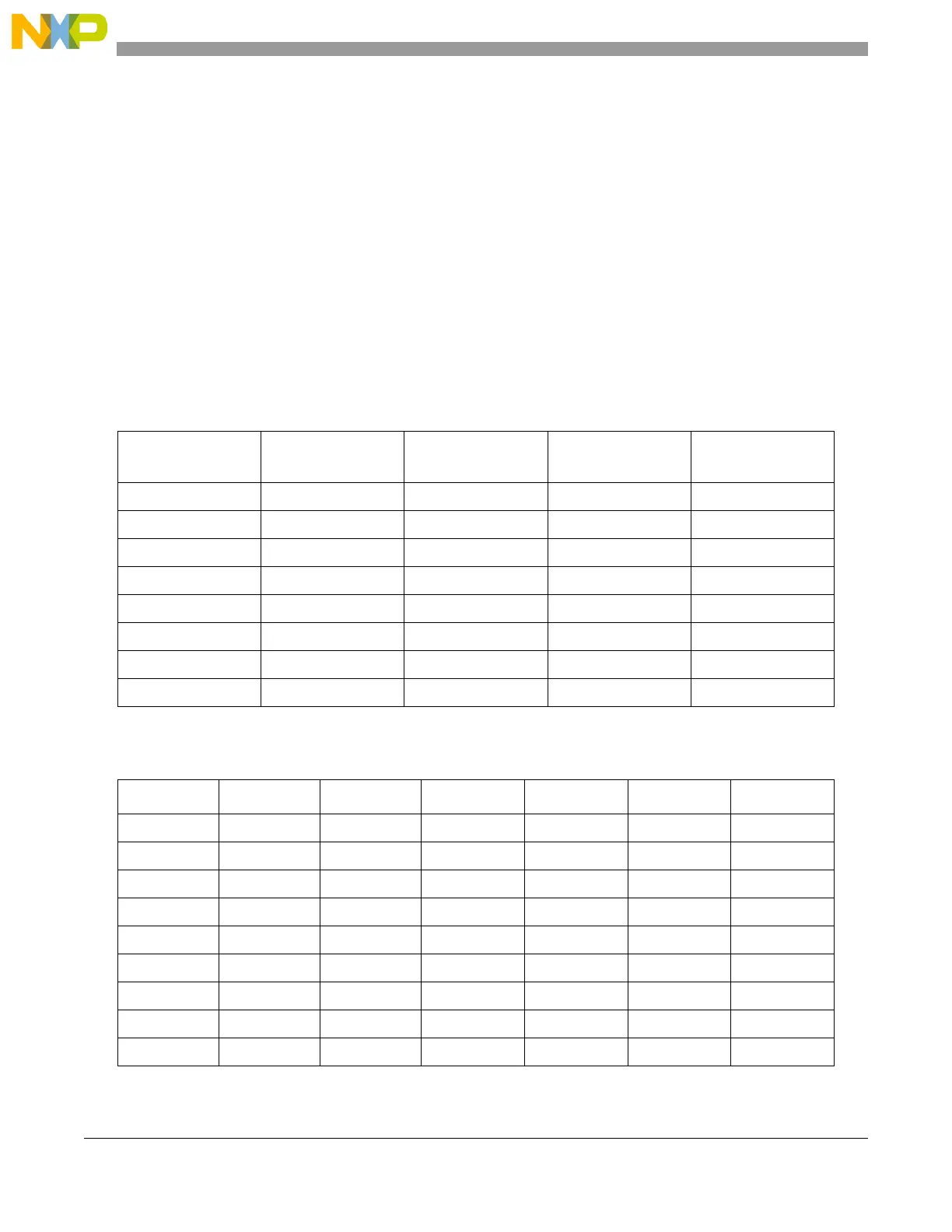

Table 5-3. ADC sampling and conversion timing

INPLATCH INPCMP INPSAMP T

sample

1

T

eval

ndelay T

conv

1 11 0000 1001 8 × Tck 30 × Tck 1 × Tck 39 × Tck

2

1 11 0000 1010 9 × Tck 30 × Tck 1 × Tck 40 × Tck

1 11 0000 1011 10 × Tck 30 × Tck 1 × Tck 41 × Tck

1 11 0000 1100 11 × Tck 30 × Tck 1 × Tck 42 × Tck

1 11 0000 1101 12 × Tck 30 × Tck 1 × Tck 43 × Tck

1 11 0000 1110 13 × Tck 30 × Tck 1 × Tck 44 × Tck

1 11 0000 1111 14 × Tck 30 × Tck 1 × Tck 45 × Tck

... ... ... ... ... ... ...

1 11 1111 1100 251 × Tck 30 × Tck 1 × Tck 282 × Tck

T

eval

10 T

biteval

10 INPCMP T

ck

==

INPCMP 1 and INPLATCH INPCMP

T

conv

T

sample

T

eval

ndelay T

ck

++=

Loading...

Loading...