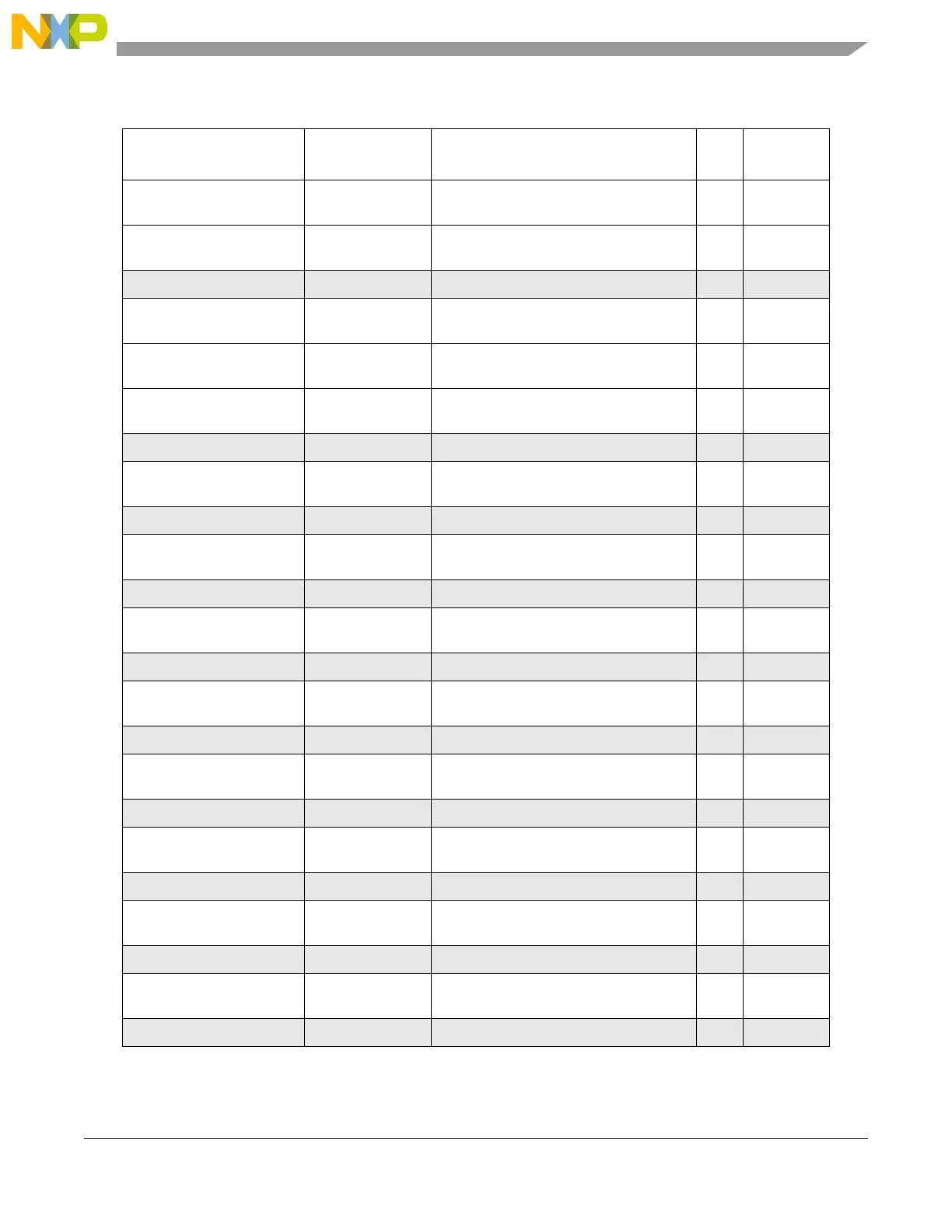

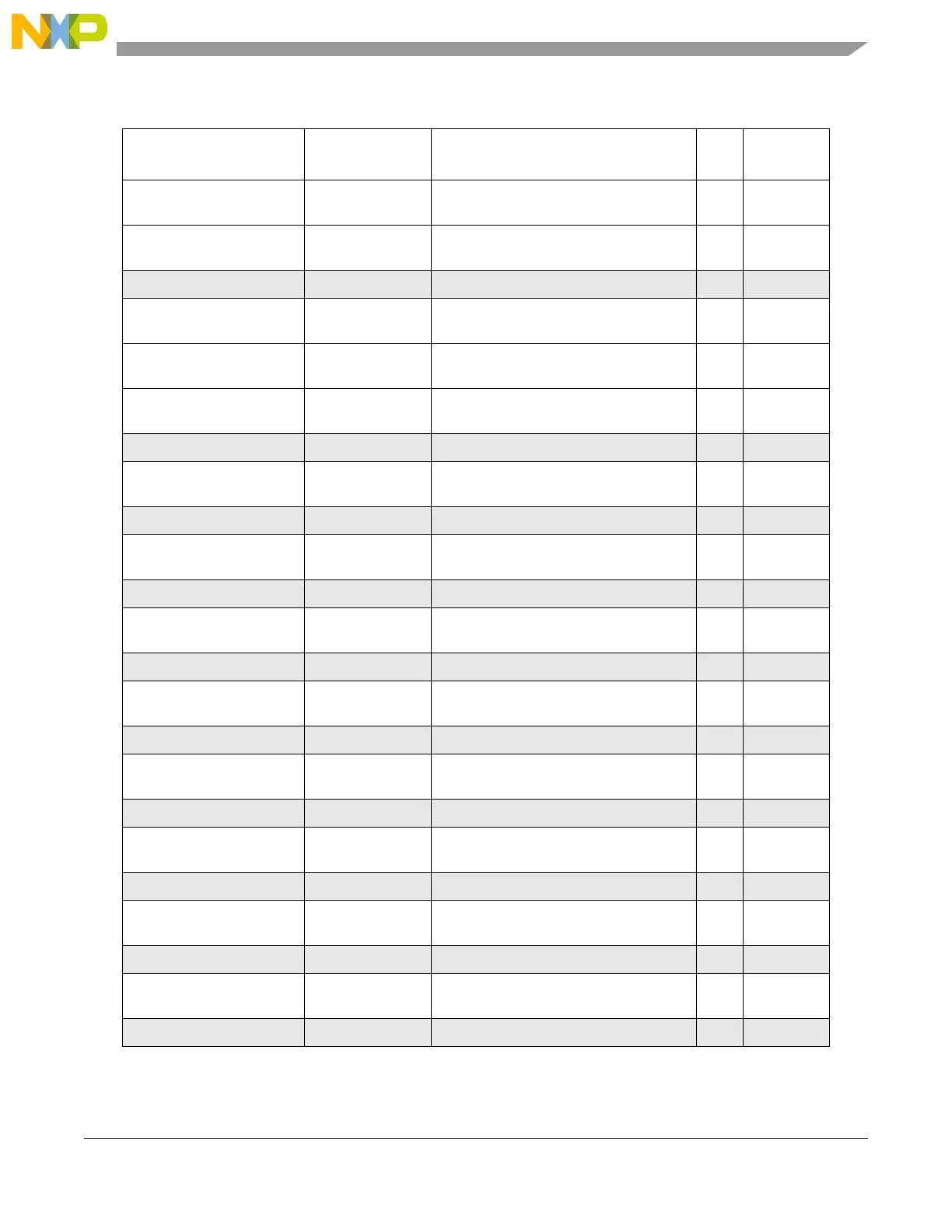

System Integration Unit Lite (SIUL)

MPC5606S Microcontroller Reference Manual, Rev. 7

Freescale Semiconductor 1189

Base + 0x0014 ISR Interrupt Status Flag Register 32-bit on page

1193

Base + 0x0018 IRER Interrupt Request Enable Register 32-bit on page

1193

Base + (0x001C–0x0027) — Reserved — —

Base + 0x0028 IREER Interrupt Rising Edge Event Enable 32-bit on page

1194

Base + 0x002C IFEER Interrupt Falling-Edge Event Enable 32-bit on page

1194

Base + 0x0030 IFER IFER Interrupt Filter Enable Register 32-bit on page

1195

Base + (0x0034–0x003F) — Reserved — —

Base + 0x0040—

Base + 0x0148

PCR0–PCR132

1

Pad Configuration Registers 0–132 16-bit on page

1195

Base + (0x014C–0x04FF) — Reserved — —

Base + 0x0500–

Base + 0x0528

PSMI0_3–

PSMI40_42

Pad Selection for Multiplexed Inputs 32-bit on page

1198

Base + (0x052C–0x05FF) — Reserved — —

Base + 0x0600–

Base + 0x0684

GPDO0_3–

GPDO132_135

1

GPIO Pad Data Output Register 32-bit on page

1202

Base + (0x0688–07FF) — Reserved — —

Base + 0x0800–

Base + 0x0884

GPDI0_3–

GPDI132_135

1

GPIO Pad Data Input Register 32-bit on page

1202

Base + (0x088C–0x0BFF) — Reserved —

Base + 0x0C00–

Base + 0x0C10

PGPDO0–

PGPDO4

Parallel GPIO Pad Data Out Register 32-bit on page

1203

Base + (0x0C14–0x0C3F) — Reserved — —

Base + 0x0C40–

Base + 0x0C50

PGPDI0–PGPDI4 Parallel GPIO Pad Data In Register 32-bit on page

1205

Base + (0x0C54–0x0C7F) — Reserved — —

Base + 0x0C80–

Base + 0x0CA4

MPGPDO0–

MPGPDO8

Masked Parallel GPIO Pad Data Out

Register

32-bit on page

1206

Base + (0x0CA8–0x0FFF) — Reserved — —

Base + 0x1000–

Base + 0x103C

IFMC0–IFMC15

1

Interrupt Filter Maximum Counter

Register

32-bit on page

1207

Base + (0x1040–0x107C) — Reserved — —

Table 37-2. SIUL memory map (continued)

Address Name Description

Size

(bits)

Location

Loading...

Loading...