Flash Memory RM0046

346/936 Doc ID 16912 Rev 5

A number of MCR bits are protected against write when another bit, or set of bits, is in a

specific state. These write locks are covered on a bit by bit basis in the preceding

description, but those locks do not consider the effects of trying to write two or more bits

simultaneously.

The Flash module does not allow the user to write bits simultaneously which would put the

device into an illegal state. This is implemented through a priority mechanism among the

bits. Table 150 shows the bit changing priorities.

If the user attempts to write two or more MCR bits simultaneously, only the bit with the

lowest priority level is written.

Low/Mid Address Space Block Locking register (LML)

The Low/Mid Address Space Block Locking register provides a means to protect blocks from

being modified. These bits, along with bits in the SLL register, determine if the block is

locked from program or erase. An “OR” of LML and SLL determine the final lock status.

Identical LML registers are provided in the code Flash and the data Flash blocks.

EHV

31

Enable High Voltage

The EHV bit enables the Flash module for a high voltage program/Erase operation. EHV is cleared

on reset.

EHV must be set after an interlock write to start a program/Erase sequence. EHV may be set under

one of the following conditions:

– Erase (ERS = 1, ESUS = 0, UT0[AIE] = 0)

– Program (ERS = 0, ESUS = 0, PGM = 1, UT0[AIE] = 0)

In normal operation, a 1-to-0 transition of EHV with DONE high and ESUS low terminates the

current program/Erase high voltage operation.

When an operation is terminated, there is a 1-to-0 transition of EHV with DONE low and the

eventual Suspend bit low. A termination causes the value of PEG to be cleared, indicating a failing

program/Erase; address locations being operated on by the terminated operation contain

indeterminate data after a termination. A suspended operation cannot be terminated. Terminating a

high voltage operation leaves the Flash module addresses in an indeterminate data state. This may

be recovered by executing an Erase on the affected blocks.

EHV may be written during Suspend. EHV must be high to exit Suspend. EHV may not be written

after ESUS is set and before DONE transitions high. EHV may not be cleared after ESUS is cleared

and before DONE transitions low.

0 Flash is not enabled to perform an high voltage operation.

1 Flash is enabled to perform an high voltage operation.

Table 149. MCR field descriptions (continued)

Field Description

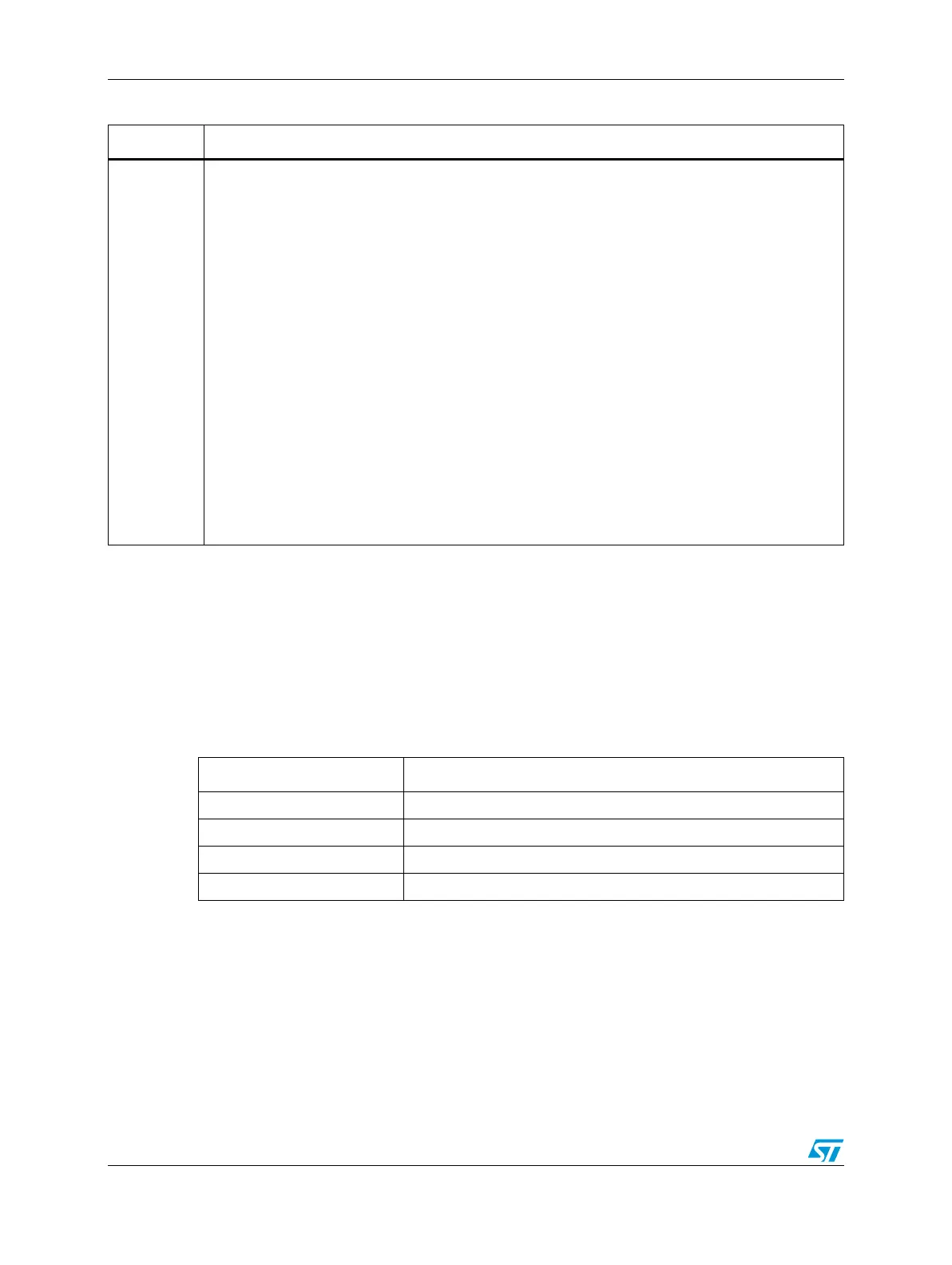

Table 150. MCR bits set/clear priority levels

Priority level MCR bits

1ERS

2PGM

3EHV

4ESUS

Loading...

Loading...