Error Correction Status Module (ECSM) RM0046

300/936 Doc ID 16912 Rev 5

Configuration Register, an ECC event in the flash causes the address, attributes and data

associated with the access to be loaded into the FEAR, FEMR, FEAT and FEDR registers,

and the appropriate flag (F1BC or FNCE) in the ECC Status Register to be asserted.

This register can only be read from the IPS programming model; any attempted write is

ignored.

Flash ECC Data Register (FEDR)

The FEDR is a 32-bit register for capturing the data associated with the last properly

enabled ECC event in the flash memory. Depending on the state of the ECC Configuration

Register, an ECC event in the flash causes the address, attributes and data associated with

the access to be loaded into the FEAR, FEMR, FEAT and FEDR registers, and the

appropriate flag (F1BC or FNCE) in the ECC Status Register to be asserted.

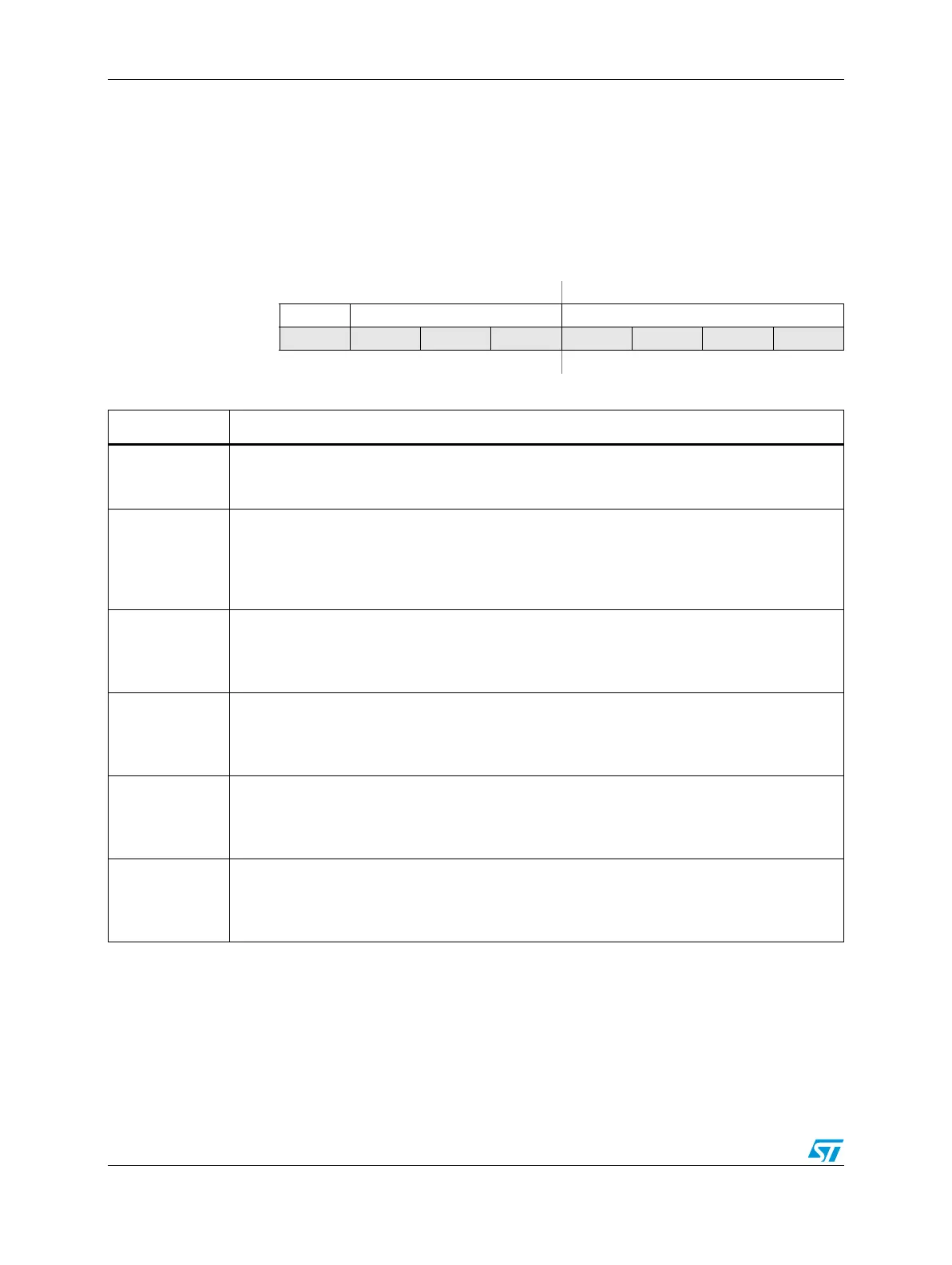

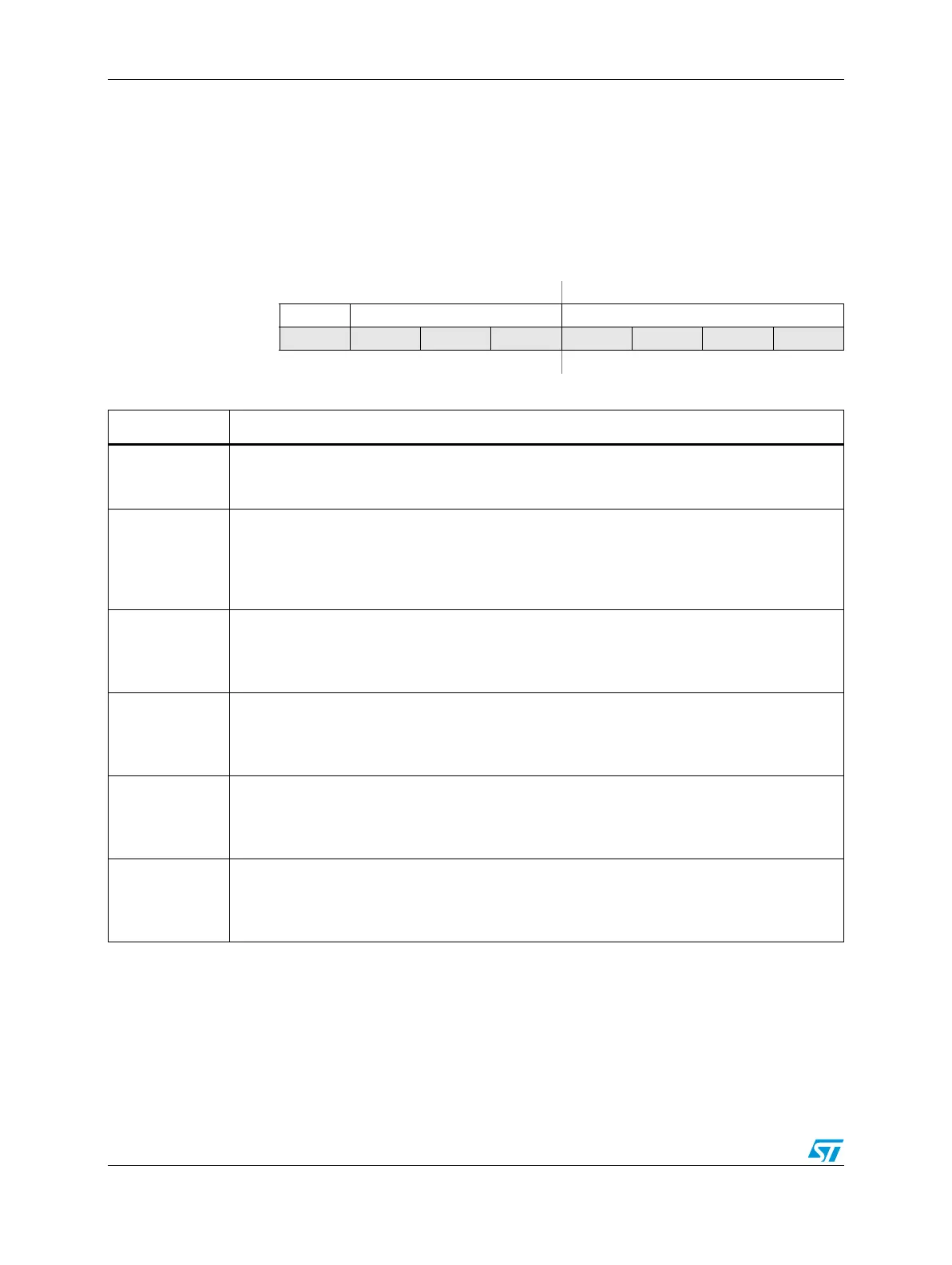

Figure 136. Flash ECC Attributes (FEAT) Register

Address: Base + 0x0057 Access: User read-only

01234567

R WRITE SIZE[2:0] PROTECTION[3:0]

W

Reset0000––––

Table 126. FEAT field descriptions

Name Description

0

WRITE

AMBA-AHB HWRITE

0 AMBA-AHB read access

1 AMBA-AHB write access

1-3

SIZE[2:0]

AMBA-AHB HSIZE[2:0]

000 8-bit AMBA-AHB access

001 16-bit AMBA-AHB access

010 32-bit AMBA-AHB access

1xx Reserved

4

PROTECTION[3]

AMBA-AHB HPROT[3]

Protection[0]: Type

0 I-Fetch

1 Data

5

PROTECTION[2]

AMBA-AHB HPROT[2]

Protection[1]: Mode

0 User mode

1 Supervisor mode

6

PROTECTION[1]

AMBA-AHB HPROT[1]

Protection[2]: Bufferable

0 Non-bufferable

1Bufferable

7

PROTECTION[0]

AMBA-AHB HPROT[0]

Protection[3]: Cacheable

0 Non-cacheable

1 Cacheable

Loading...

Loading...