RM0046 Clock Description

Doc ID 16912 Rev 5 115/936

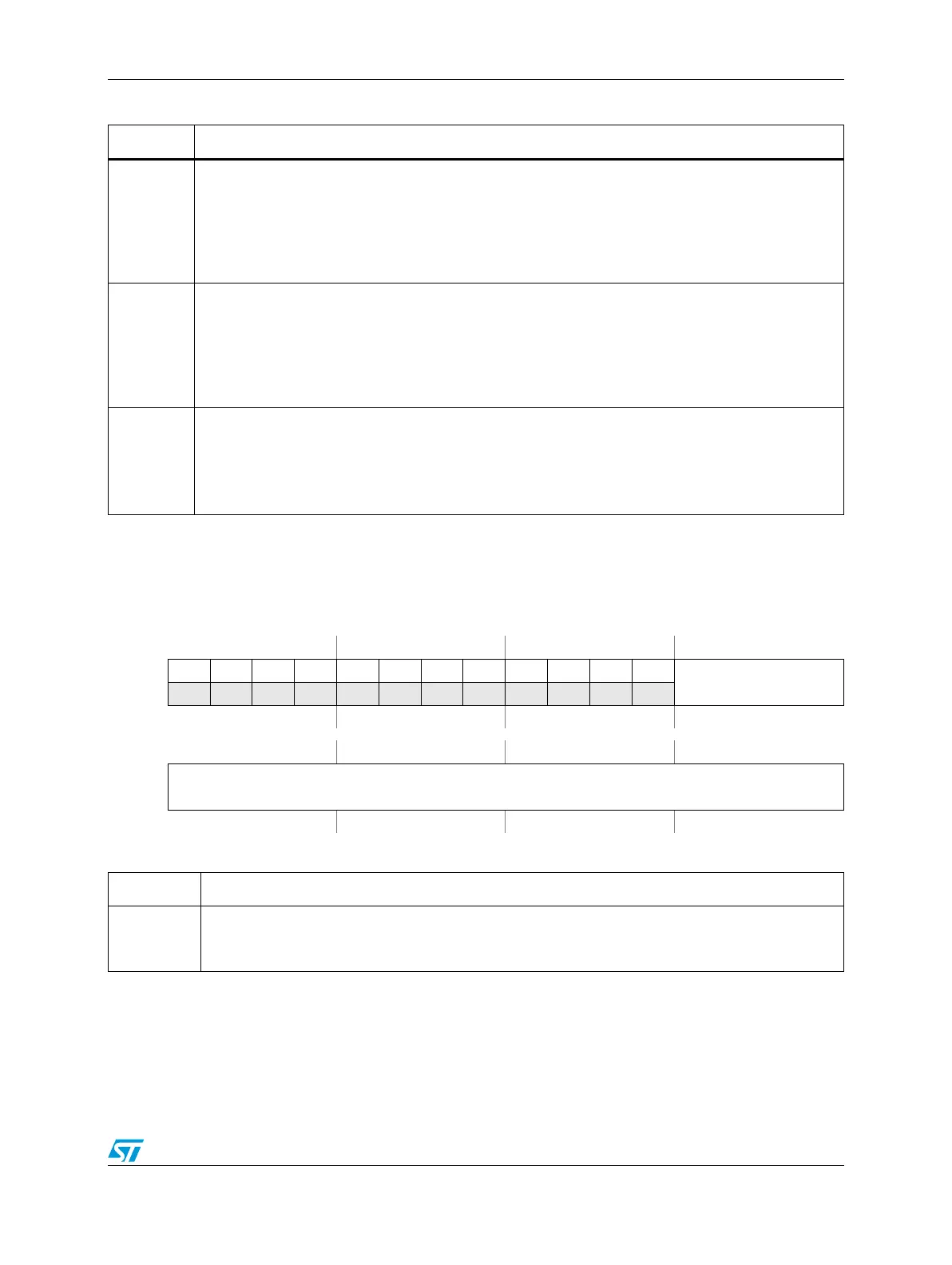

Measurement Duration Register (CMU_0_MDR)

FHHI_0

FMPLL_0 Clock frequency higher than high reference interrupt

This bit is set by hardware when CK_FMPLL_ 0 frequency becomes higher than HFREF_A value and

CK_FMPLL_0 is ‘ON’ and the PLL locked as signaled by the ME. It can be cleared by software by

writing 1.

0: No FHH event

1: FHH event pending

FLLI_0

FMPLL_0 Clock frequency less than low reference event

This bit is set by hardware when CK_FMPLL_0 frequency becomes lower than LFREF_A value and

CK_FMPLL_0 is ‘ON’ and the PLL locked as signaled by the ME. It can be cleared by software by

writing 1.

0: No FLL event

1: FLL event pending

OLRI

Oscillator frequency less than RC frequency event

This bit is set by hardware when the frequency of CK_XOSC is less than CK_IRC/2

RCDIV

frequency

and CK_XOSC is ‘ON’ and stable as signaled by the ME. It can be cleared by software by writing 1.

0: No OLR event

1: OLR event pending

Table 22. CMU_0_ISR field descriptions (continued)

Field Description

Figure 25. Measurement Duration Register (CMU_0_MDR)

Address:

Base + 0x0018 Access: User read/write

0123456789101112131415

R00000000 0000

MD[19:16]

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

MD[15:0]

W

Reset0000000000000000

Table 23. CMU_0_MDR field descriptions

Field Description

MD[19:0]

Measurement duration bits

This register displays the measured duration in term of IRC clock cycles. This value is loaded in the

frequency meter downcounter. When SFM bit is set to ‘1’, downcounter starts counting.

Loading...

Loading...