Analog-to-Digital Converter (ADC) RM0046

590/936 Doc ID 16912 Rev 5

Main Status Register (MSR)

The Main Status Register (MSR) provides status bits for the ADC.

ABORT

Abort Conversion

When this bit is set, the ongoing conversion is aborted and a new conversion is invoked. This

bit is reset by hardware as soon as a new conversion is invoked. If it is set during a scan chain,

only the ongoing conversion is aborted and the next conversion is performed as planned.

0 Conversion is not affected

1 Aborts the ongoing conversion

ACKO

Auto-clock-off enable

If set, this bit enables the Auto clock off feature.

0 Auto clock off disabled

1 Auto clock off enabled

PWDN

Power-down enable

When this bit is set, the analog module is requested to enter Power Down mode. When ADC

status is PWDN, resetting this bit starts ADC transition to IDLE mode.

0 ADC is in normal mode

1 ADC has been requested to power down

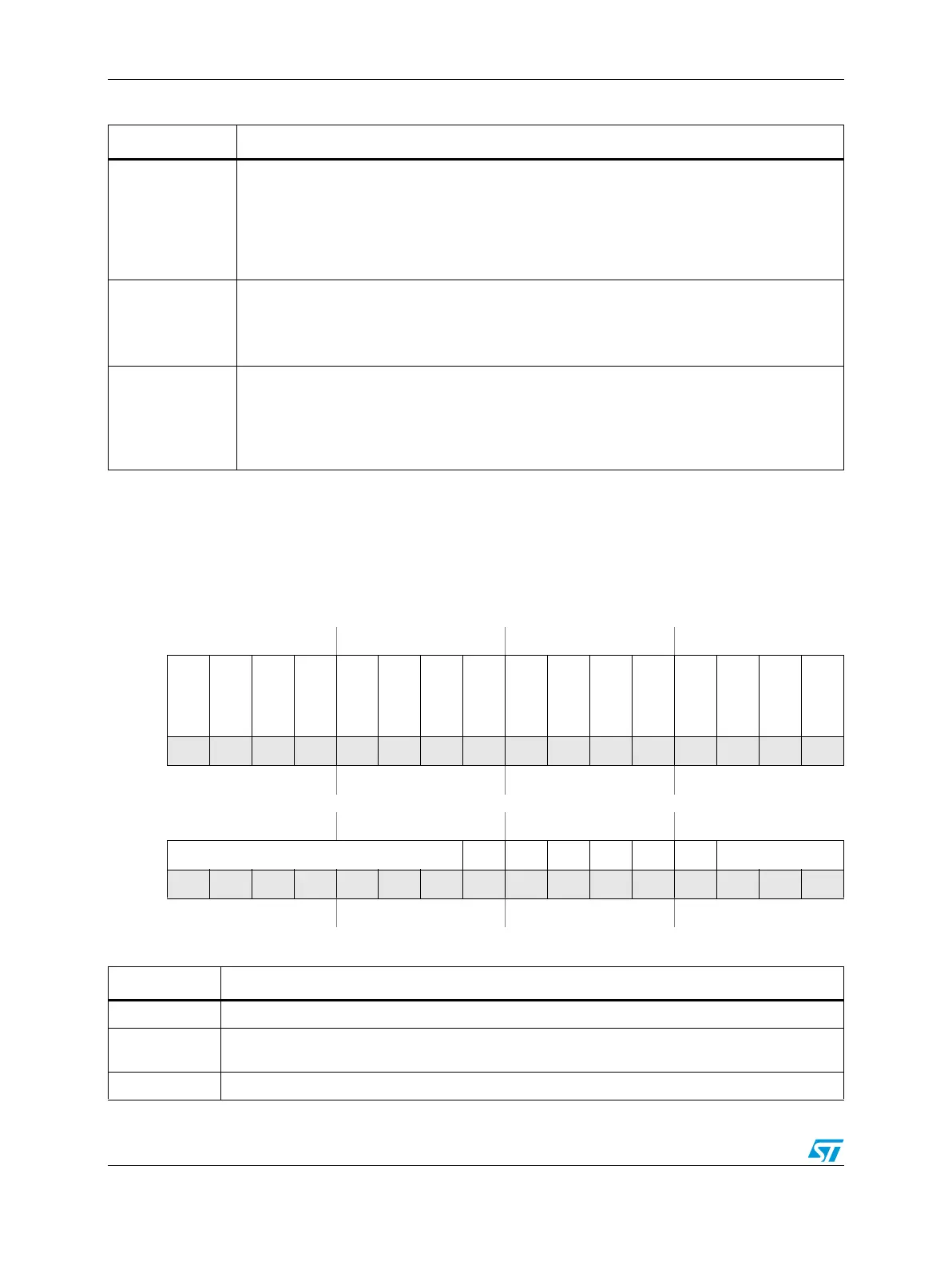

Table 295. MCR field descriptions (continued)

Field Description

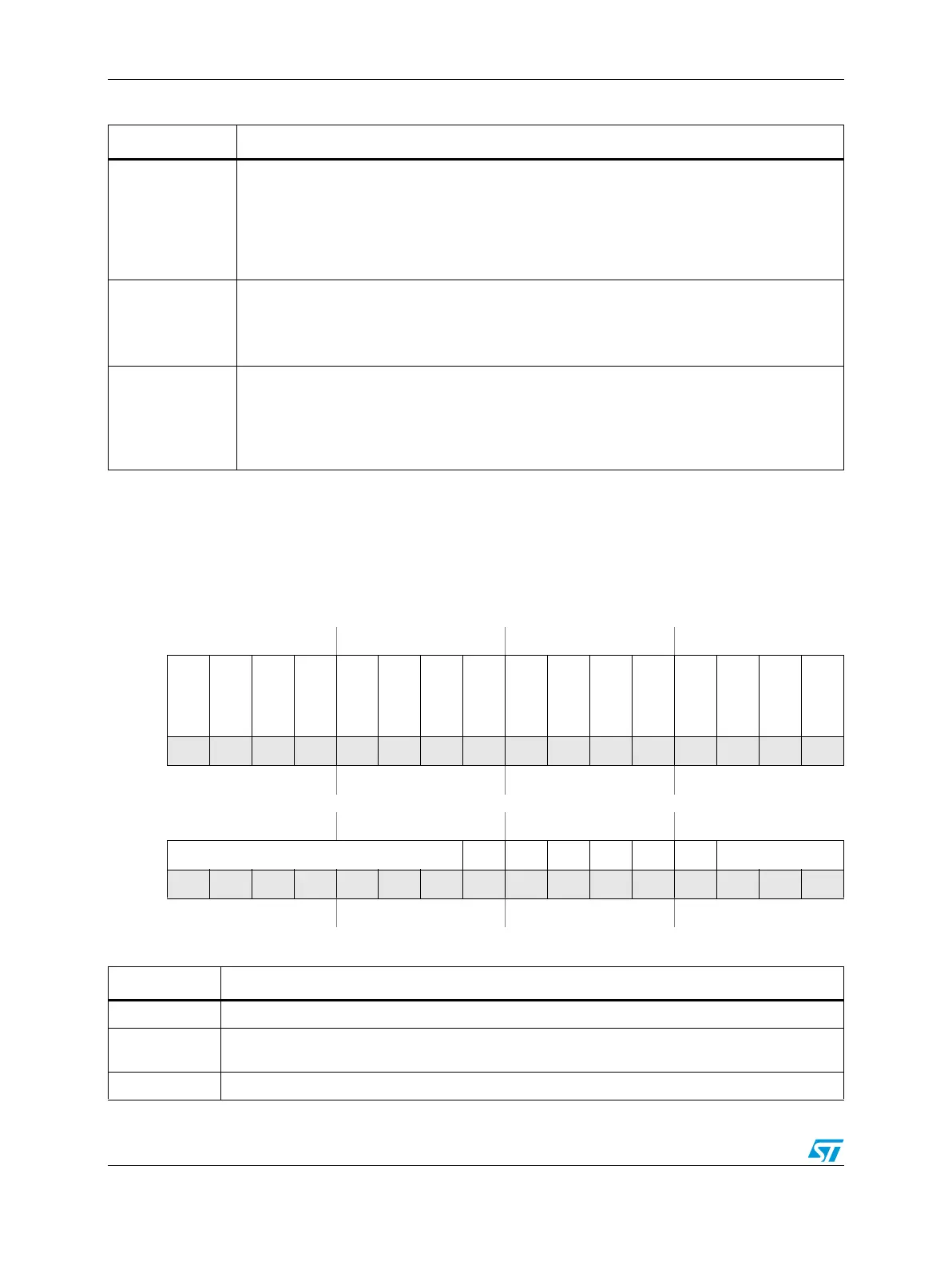

Figure 286. Main Status Register (MSR)

Address:

Base + 0x0004 Access: User read-only

0123456789101112131415

R0000000

NSTART

JABORT

00

JSTART

0 00

CTUSTART

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R CHADDR 0 00

ACK0

0 0 ADCSTATUS

W

Reset0000000000000001

Table 296. MSR field descriptions

Field Description

NSTART This status bit is used to signal that a Normal conversion is ongoing.

JABORT

This status bit is used to signal that an Injected conversion has been aborted. This bit is reset

when a new injected conversion starts.

JSTART This status bit is used to signal that an Injected conversion is ongoing.

Loading...

Loading...