RM0046 eTimer

Doc ID 16912 Rev 5 719/936

Status register (STS)

Table 375. CTRL3 field descriptions

Field Description

STPEN

Stop Actions Enable

This bit allows the tristating of the timer output during stop mode.

0 Output enable is unaffected by stop mode.

1 Output enable is disabled during stop mode.

ROC

Reload on Capture

These bits enable the capture function to cause the counter to be reloaded from the LOAD register.

00 Do not reload the counter on a capture event.

01 Reload the counter on a capture 1 event.

10 Reload the counter on a capture 2 event.

11 Reload the counter on both a capture 1 event and a capture 2 event.

C2FCNT

CAPT2 FIFO Word Count

This field reflects the number of words in the CAPT2 FIFO.

C1FCNT

CAPT1 FIFO Word Count

This field reflects the number of words in the CAPT1 FIFO.

DBGEN

Debug Actions Enable

These bits allow the counter channel to perform certain actions in response to the device entering

debug mode.

00 Continue with normal operation during debug mode. (default)

01 Halt channel counter during debug mode.

10 Force OFLAG to logic 0 (prior to consideration of the OPS bit) during debug mode.

11 Both halt counter and force OFLAG to 0 during debug mode.

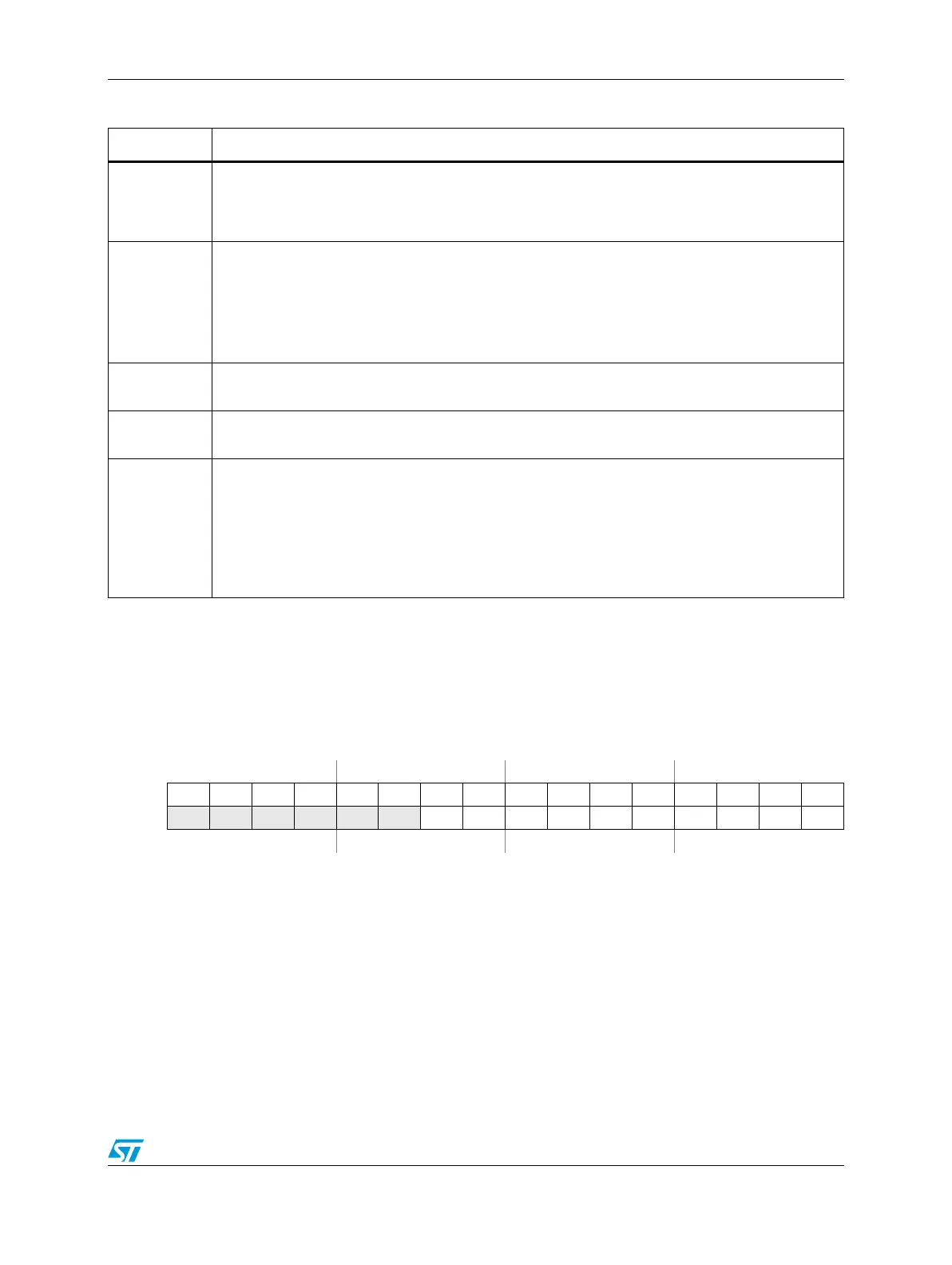

Figure 402. Status register (STS)

Address:

Base + 0x0014 (eTimer0)

Base + 0x0034 (eTimer1)

Base + 0x0054 (eTimer2)

Base + 0x0074 (eTimer3)

Base + 0x0094 (eTimer4)

Base + 0x00B4 (eTimer5)

Access: User read/write

0123456789101112131415

R000000WDFRCFICF2ICF1IEHFIELFTOFTCF2TCF1TCF

W

w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Loading...

Loading...