Enhanced Direct Memory Access (eDMA) RM0046

386/936 Doc ID 16912 Rev 5

18.5.2 Register descriptions

Read operations on reserved bits in a register return undefined data. Do not write

operations to reserved bits. Writing to reserved bits in a register can generate errors. The

maximum register bit-width for this device is 16 bits wide.

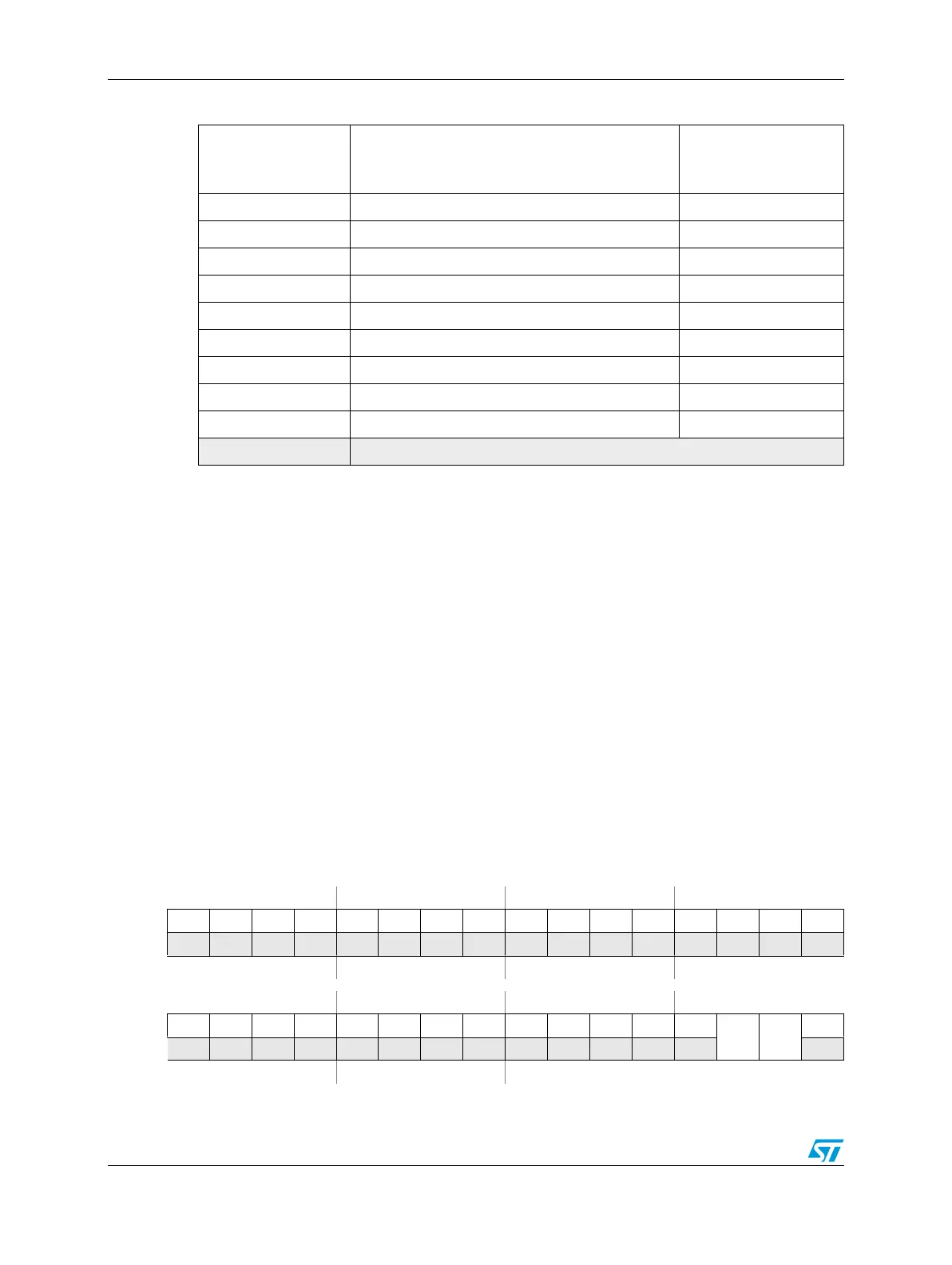

eDMA Control Register (EDMA_CR)

The 32-bit EDMA_CR defines the basic operating configuration of the eDMA.

The eDMA arbitrates channel service requests in one group of 16 channels.

Arbitration can be configured to use either fixed-priority or round-robin. In fixed-priority

arbitration, the highest priority channel requesting service is selected to execute. The

priorities are assigned by the channel priority registers. In round-robin arbitration mode, the

channel priorities are ignored and the channels are cycled through, from channel 15 down

to channel 0, without regard to priority.

Refer to Section , “eDMA Channel n Priority Registers (EDMA_CPRn).

0x10E0 TCD07—Transfer Control Descriptor 7 on page 18-399

0x1100 TCD08—Transfer Control Descriptor 8 on page 18-399

0x1120 TCD09—Transfer Control Descriptor 9 on page 18-399

0x1140 TCD10—Transfer Control Descriptor 10 on page 18-399

0x1160 TCD11—Transfer Control Descriptor 11 on page 18-399

0x1180 TCD12—Transfer Control Descriptor 12 on page 18-399

0x11A0 TCD13—Transfer Control Descriptor 13 on page 18-399

0x11C0 TCD14—Transfer Control Descriptor 14 on page 18-399

0x11E0 TCD15—Transfer Control Descriptor 15 on page 18-399

0x1200

–0x3FFF

Reserved

Table 175. eDMA memory map (continued)

Offset from

EDMA_BASE

(0xFFF4_4000)

Register Location

Figure 177. eDMA Control Register (EDMA_CR)

Address:

Base + 0x0000 Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0 0 0 0 0 0 0 0

ERCA

EDBG

0

W

Reset0000000000000000

Loading...

Loading...