RM0046 Nexus Development Interface (NDI)

Doc ID 16912 Rev 5 865/936

36.10.3 Linked Instruction Address and Data Address Compare Event

Data Address Compare debug events may be ‘linked’ with an Instruction Address Compare

event by setting the DAC1LNK and/or DAC2LNK control bits in DBCR2 to further refine

when a Data Address Compare debug event is generated. DAC1 may be linked with IAC1,

and DAC2 (when not used as a mask or range bounds register) may be linked with IAC3.

When linked, a DAC1 (or DAC2) debug event occurs when the same instruction which

generates the DAC1 (or DAC2) ‘hit’ also generates an IAC1 (or IAC3) ‘hit’. When linked, the

IAC1 (or IAC3) event is not recorded in the Debug Status register, regardless of whether a

corresponding DAC1 (or DAC2) event occurs, or whether the IAC1 (or IAC3) event enable is

set.

When enabled and execution of a load or store class instruction results in a data access with

an address that meets the criteria specified in the DBCR0, DBCR2, DBCR4, DAC1, DAC2,

DVC1, and DVC2 Registers, and the instruction also meets the criteria for generating an

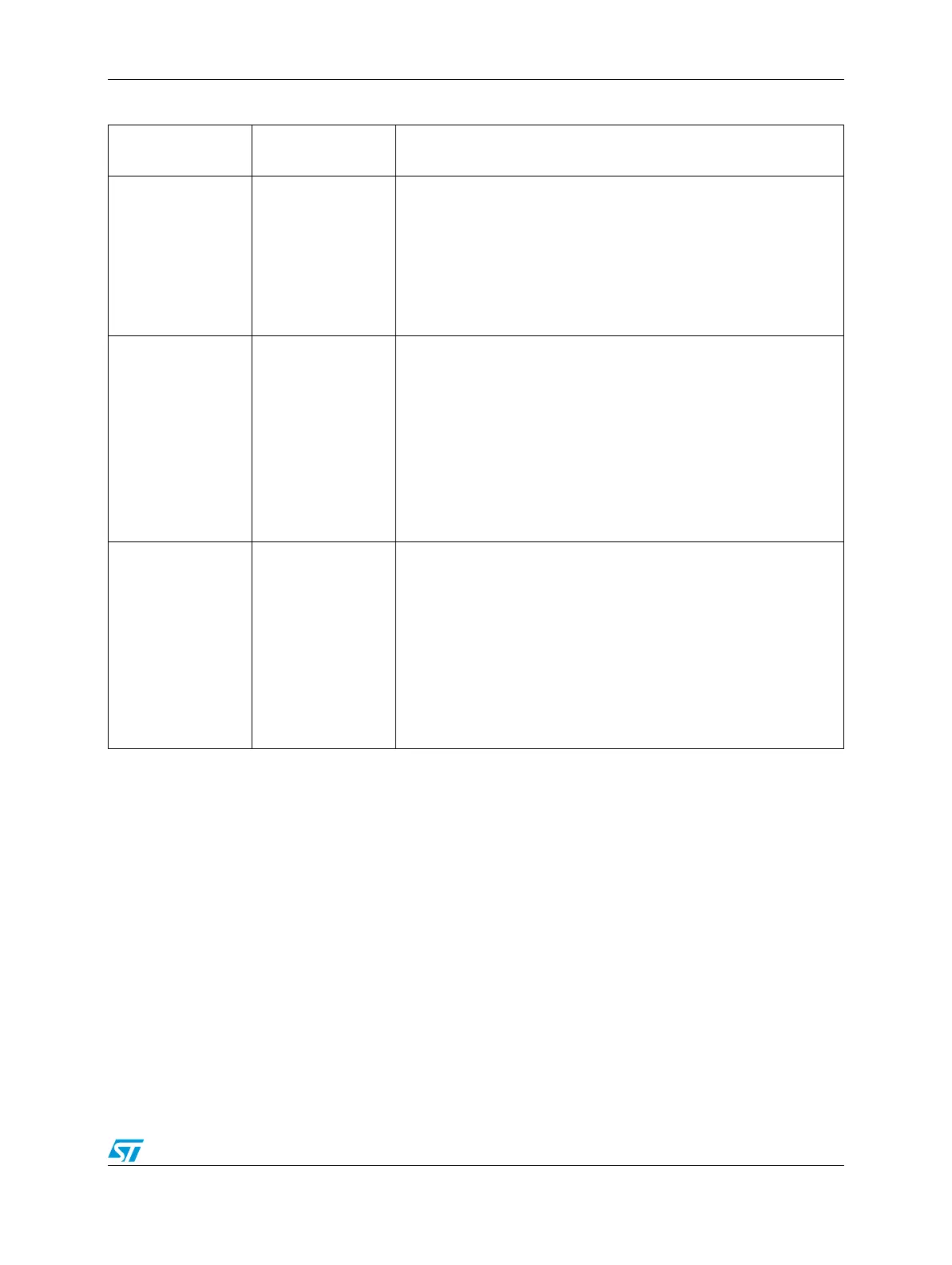

DVC DACx DSI, with DACy

(1)

Take Debug exception, DBSR update setting DACx. DAC_OFST not

set. DSRR0 points to 2nd load/store class instruction. No MASx

register update. No ESR update. No debug counter update occurs

for the 2nd ld/st.

Note: in this case the 2nd ld/st exception is masked. This

behavior is implementation dependent and may differ on other

CPUs.

DVC DACx DACy

Take Debug exception, DBSR update setting DACx, DACy.

DAC_OFST set to 2’b01. DSRR0 points to instruction after 2nd

load/store class instruction. Debug counter update occurs for the 2nd

ld/st as appropriate.

Note: in this case debug counter updates can occur for the 2nd

ld/st even though the 1st ld/st has a DVC DAC exception.

Note: in this case if x==y, then the resultant state of DBSR and

DSRR0 may be indistinguishable from the “no DACy” case.

DVC DACx DVC DACy

Take Debug exception, DBSR update setting DACx, DACy.

DAC_OFST set to 2’b01. DSRR0 points to instruction after 2nd

load/store class instruction. Debug counter update occurs for the 2nd

ld/st as appropriate.

Note: in this case debug counter updates occur for the 2nd ld/st

even though the 1st ld/st has a DVC DAC exception.

Note: in this case if x==y, then the resultant state of DBSR and

DSRR0 may be indistinguishable from the “no DACy” case.

1. No DVC can occur since load/store operation not performed. For the case that an earlier transfer in a 2nd ldst class lmw or

stmw sequence successfully caused a DACy or DVC DACy, the DACy or DVC DACy is also ignored, unlike in the case

where the lmw or stmw was the 1st load/store classes and an earlier transfer in a lmw or stmw sequence successfully

caused a DAC or DVC.

Table 458. DAC events and Resultant Updates (continued)

1st load/store

class instruction

2nd load/store

class instruction

Result

Loading...

Loading...