FlexPWM RM0046

660/936 Doc ID 16912 Rev 5

Status register (STS)

6

POLB

PWMB Output Polarity

This bit inverts the PWMB output polarity.

0 PWMB output not inverted. A high level on the PWMB pin represents the “on” or “active” state.

1 PWMB output inverted. A low level on the PWMB pin represents the “on” or “active” state.

7

POLX

PWMX Output Polarity

This bit inverts the PWMX output polarity.

0 PWMX output not inverted. A high level on the PWMX pin represents the “on” or “active” state.

1 PWMX output inverted. A low level on the PWMX pin represents the “on” or “active” state.

10:11

PWMAFS

PWMA Fault State

These bits determine the fault state for the PWMA output during fault conditions and STOP mode.

It may also define the output state during WAIT/HALT and DEBUG modes depending on the

settings of WAITEN and DBGEN.

00 Output is forced to logic 0 state prior to consideration of output polarity control.

01 Output is forced to logic 1 state prior to consideration of output polarity control.

1x Output is tristated.

12:13

PWMBFS

PWMB Fault State

These bits determine the fault state for the PWMB output during fault conditions and STOP mode.

It may also define the output state during WAIT/HALT and DEBUG modes depending on the

settings of WAITEN and DBGEN.

00 Output is forced to logic 0 state prior to consideration of output polarity control.

01 Output is forced to logic 1 state prior to consideration of output polarity control.

1x Output is tristated.

14:15

PWMXFS

PWMX Fault State

These bits determine the fault state for the PWMX output during fault conditions and STOP mode.

It may also define the output state during WAIT/HALT and DEBUG modes depending on the

settings of WAITEN and DBGEN.

00 Output is forced to logic 0 state prior to consideration of output polarity control.

01 Output is forced to logic 1 state prior to consideration of output polarity control.

1x Output is tristated.

Table 347. OCTRL field descriptions (continued)

Field Description

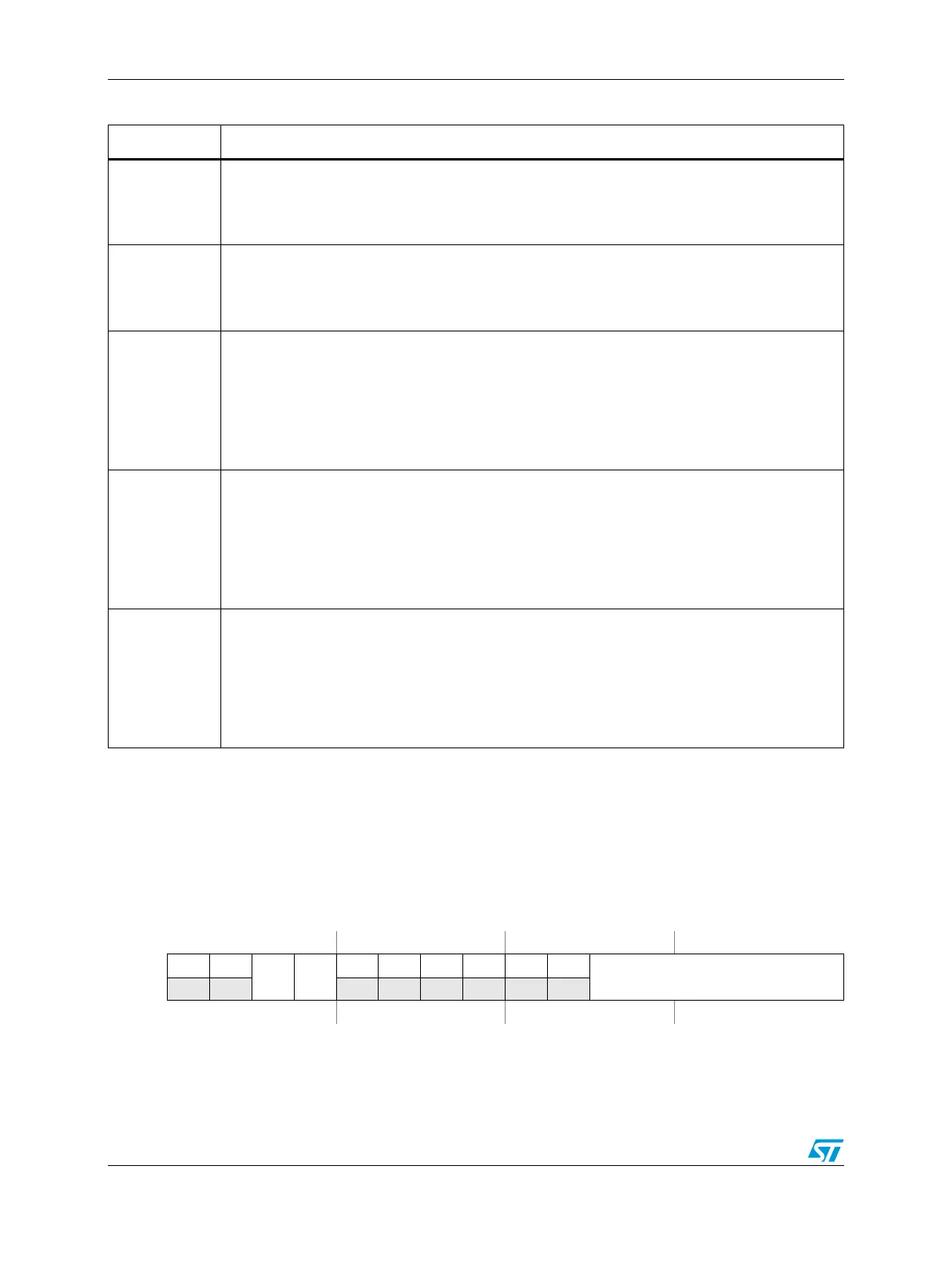

Figure 346. Status register (STS)

Address:

Base + 0x001A (Submodule 0)

Base + 0x006A (Submodule 1)

Base + 0x00BA (Submodule 2)

Base + 0x010A (Submodule 3) Access: User read/write

0123456789101112131415

R0 RUF

REF RF

000000

CMPF

W

Reset0000000000000000

Loading...

Loading...