Cross Triggering Unit (CTU) RM0046

636/936 Doc ID 16912 Rev 5

24.8.15 FIFO Right aligned data x (x = 0,...,3) (FRx)

FULL2

FIFO 2 Full interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

OR1

FIFO 1 Overrun interrupt flag

A read of this bit clears it.

0Interrupt has not occurred.

1 Interrupt has occurred.

OF1

FIFO 1 threshold Overflow interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

EMP1

FIFO 1 Empty interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

FULL1

FIFO 1 Full interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

OR0

FIFO 0 Overrun interrupt flag

A read of this bit clears it.

0 Interrupt has not occurred.

1 Interrupt has occurred.

OF0

FIFO 0 threshold Overflow interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

EMP0

FIFO 0 Empty interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

FULL0

FIFO 0 Full interrupt flag

0 Interrupt has not occurred.

1 Interrupt has occurred.

Table 331. FST field descriptions (continued)

Field Description

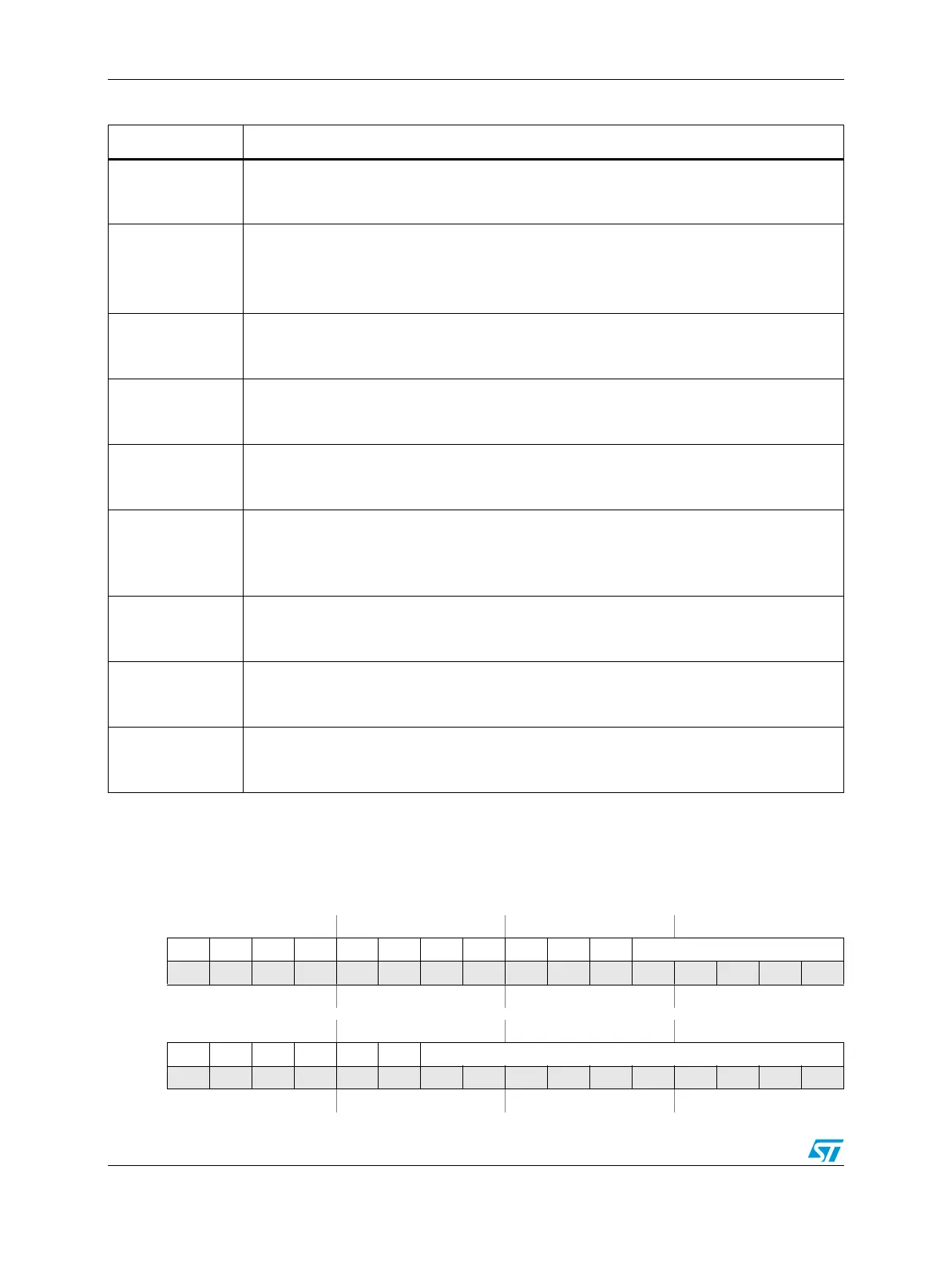

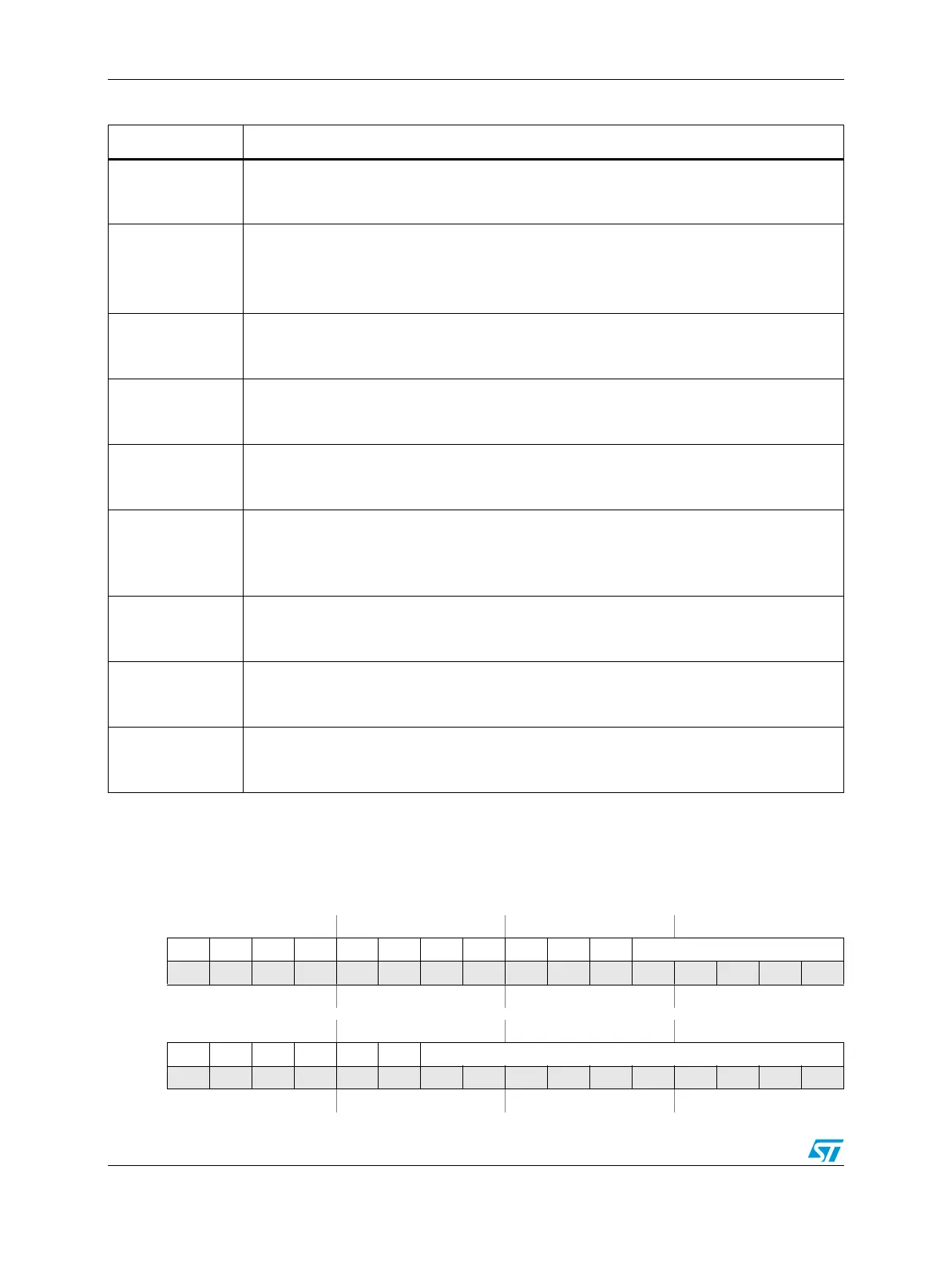

Figure 324. FIFO Right aligned data x (x = 0,...,3) (FRx)

Address:

Base + 0x0080,...,0x008C Access: User read-only

0123456789101112131415

R00000000 0 0 0 N_CH[4:0]

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R000000 DATA

W

Reset0000000000000000

Loading...

Loading...