RM0046 eTimer

Doc ID 16912 Rev 5 733/936

generation has the advantage of allowing almost any desired PWM frequency and/or

constant on or off periods. This mode of operation is often used to drive PWM amplifiers

used to power motors and inverters. The CMPLD1 and CMPLD2 registers are especially

useful for this mode, as they allow the programmer time to calculate values for the next

PWM cycle while the PWM current cycle is underway.

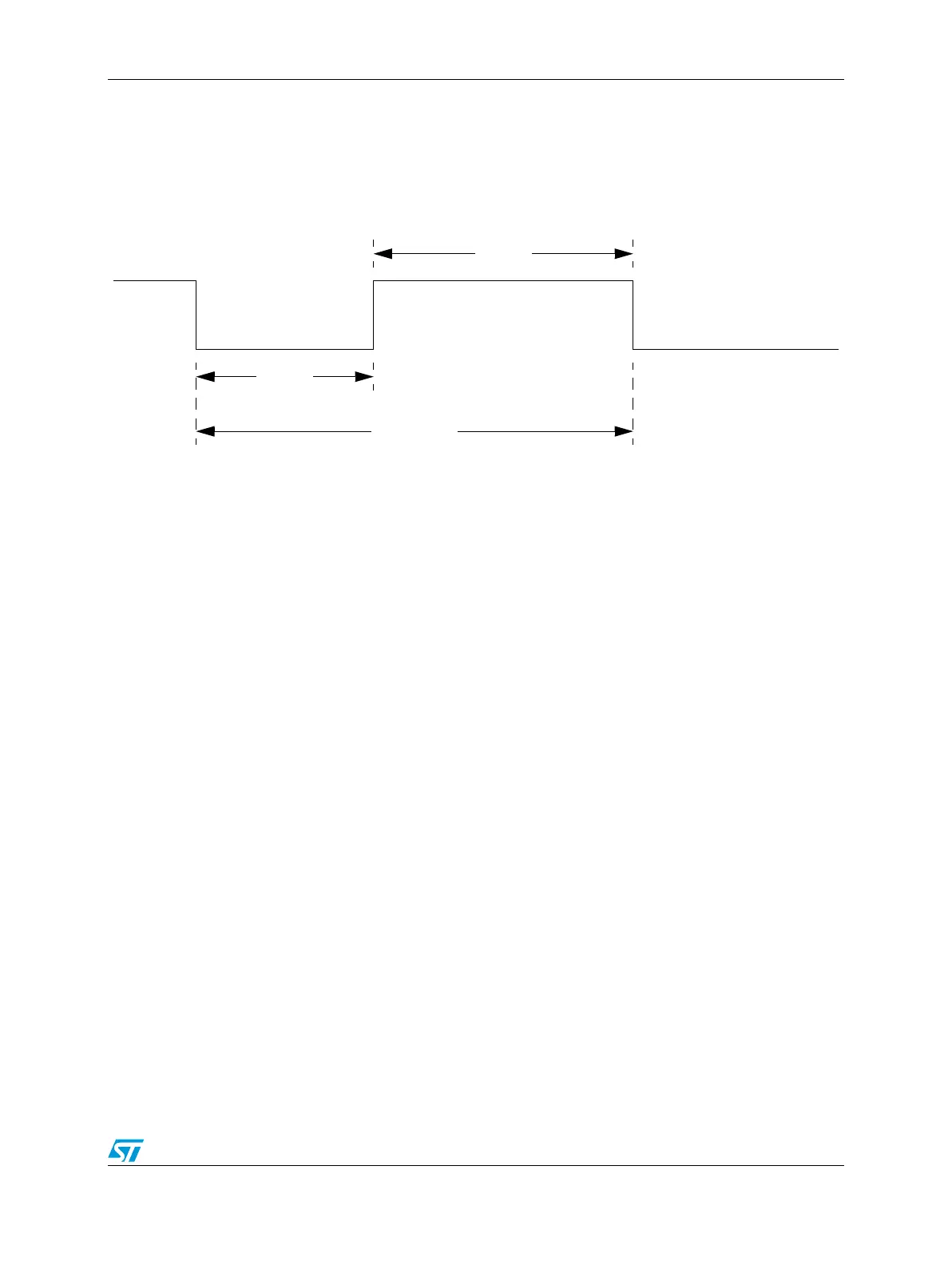

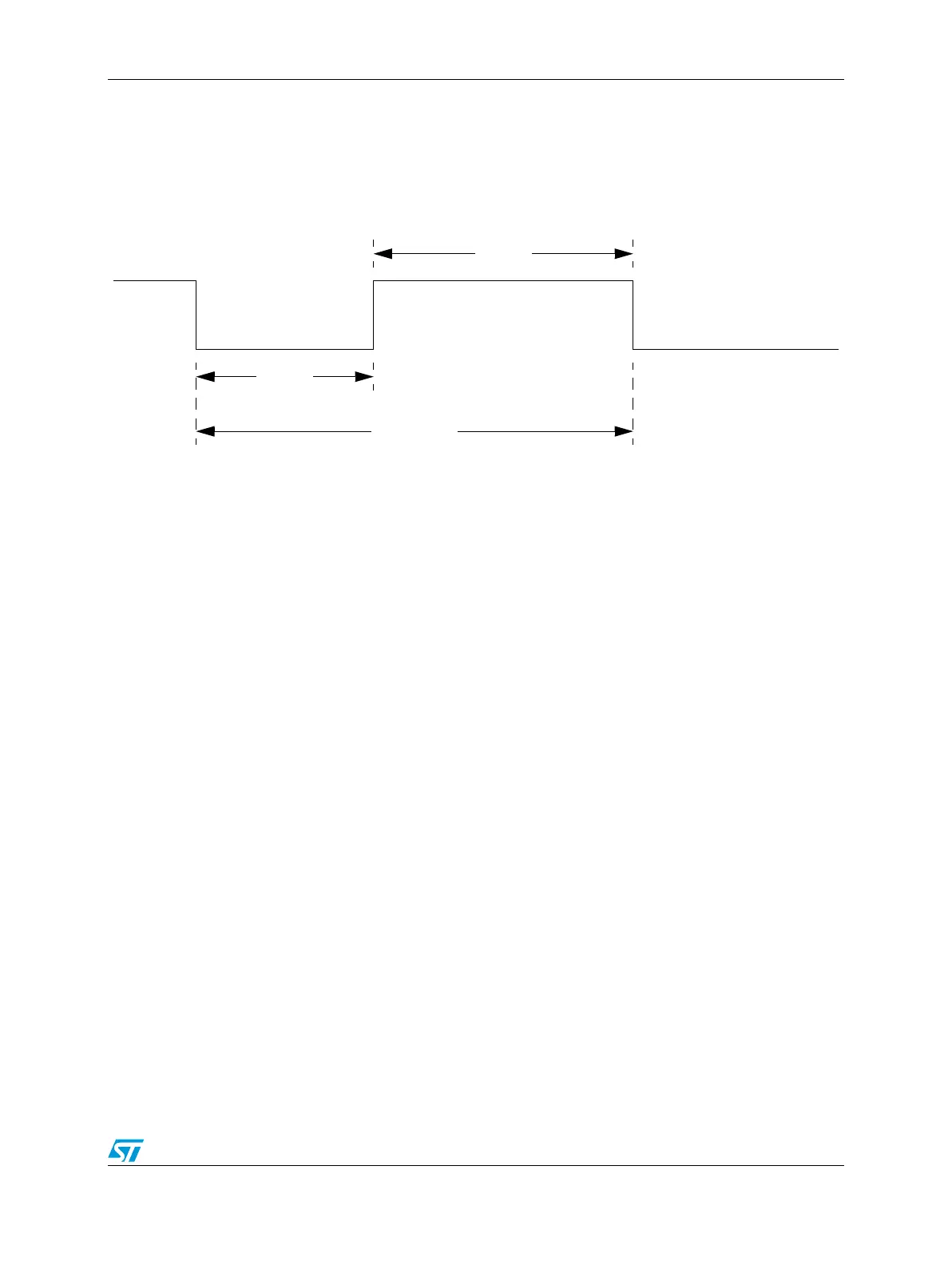

Figure 417. Variable PWM waveform

Usage of compare registers

The dual compare registers (COMP1 and COMP2) provide a bidirectional modulo count

capability.

The COMP1 register should be set to the desired maximum count value or 0xFFFF to

indicate the maximum unsigned value prior to roll-over, and the COMP2 register should be

set to the minimum count value or 0x0000 to indicate the minimum unsigned value prior to

roll-under.

When the output mode is set to 0100, the OFLAG will toggle while using alternating

compare registers. In this variable frequency PWM mode, the COMP2 value defines the

desired pulse width of the on time, and the COMP1 register defines the off time. COMP1 is

used when OFLAG == 0 and COMP2 is used when OFLAG == 1.

Use caution when changing COMP1 and COMP2 while the counter is active. If the counter

has already passed the new value, it will count to 0xFFFF or 0x0000, roll over, then begin

counting toward the new value. The check is: CNTR = COMPx, not CNTR > COMP1 or

CNTR < COMP2.

Using the CMPLD1 and CMPLD2 registers to preload compare values helps to minimize

this problem.

Usage of Compare Load registers

The CMPLD1, CMPLD2, and CCCTRL registers offer a high degree of flexibility for loading

compare registers with user-defined values on different compare events. To ensure correct

functionality while using these registers, the following methods are recommended.

The purpose of the compare load feature is to allow quicker updating of the compare

registers. A compare register can be updated using interrupts. However, because of the

latency between an interrupt event occurring and the service of that interrupt, there is the

possibility that the counter may have already counted past the new compare value by the

Loading...

Loading...