Interrupt Controller (INTC) RM0046

232/936 Doc ID 16912 Rev 5

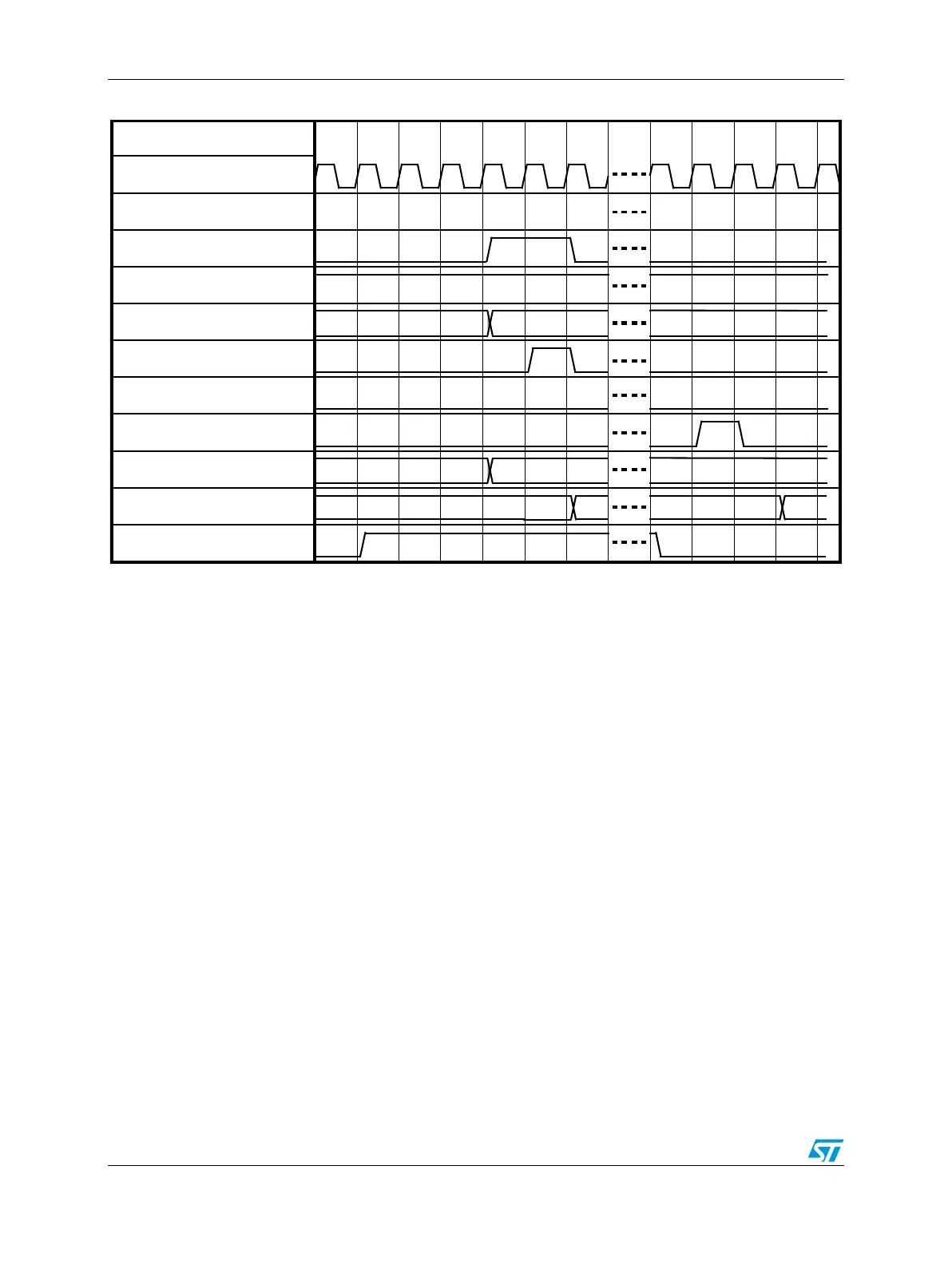

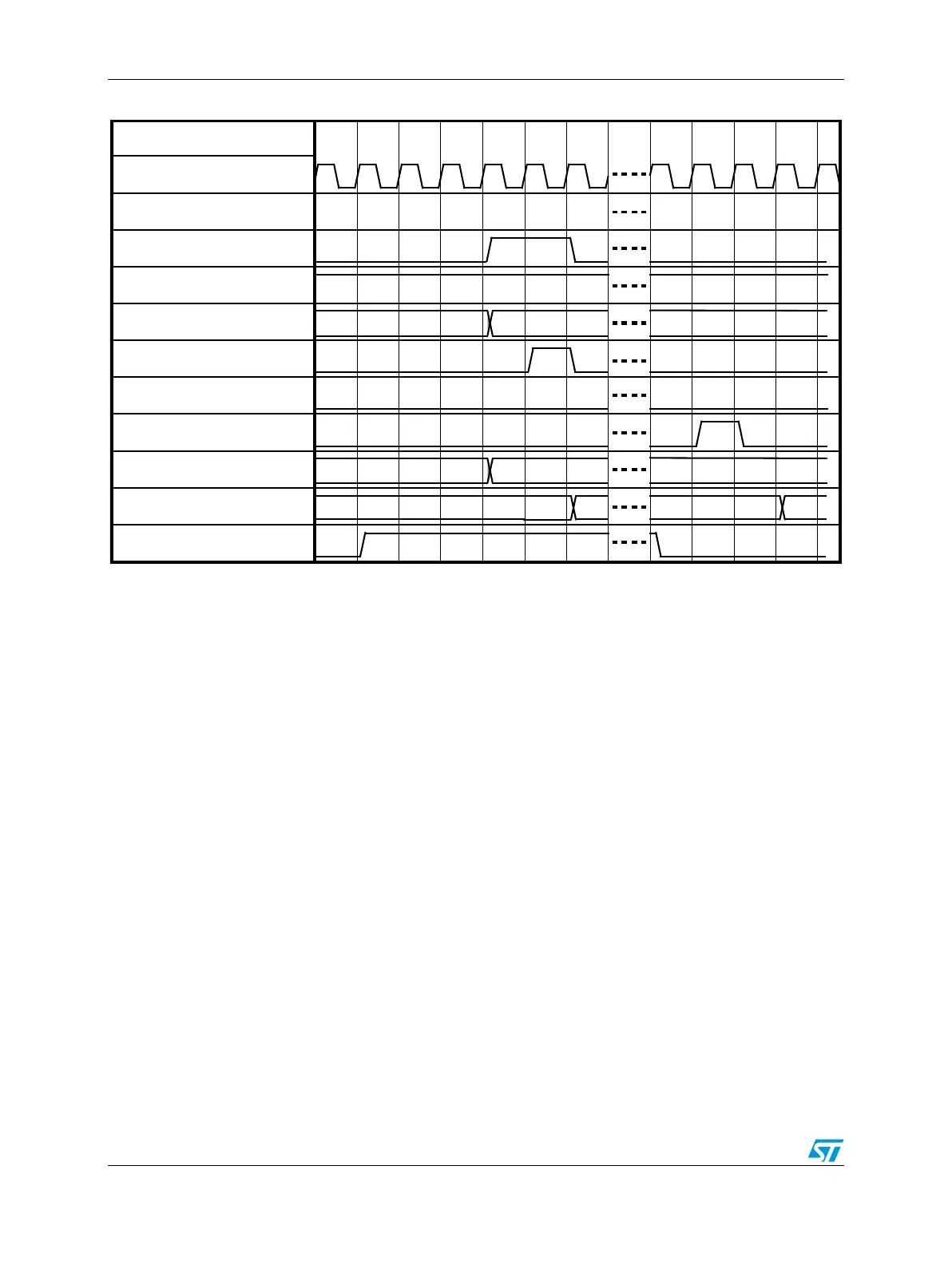

Figure 87. Hardware vector mode handshaking timing diagram

9.7 Initialization/application information

9.7.1 Initialization flow

After exiting reset, all of the PRIn fields in INTC Priority Select Registers (INTC_PSR0_3–

INTC_PSR220_221) will be zero, and PRI in INTC current priority register (INTC_CPR) will

be 15. These reset values will prevent the INTC from asserting the interrupt request to the

processor. The enable or mask bits in the peripherals are reset such that the peripheral

interrupt requests are negated. An initialization sequence for allowing the peripheral and

software settable interrupt requests to cause an interrupt request to the processor is:

interrupt_request_initialization:

interrupt_request_initialization:

configure VTES and HVEN in INTC_MCR

configure VTBA in INTC_IACKR

raise the PRIn fields in INTC_PSRn

set the enable bits or clear the mask bits for the peripheral interrupt

requests

lower PRI in INTC_CPR to zero

enable processor recognition of interrupts

9.7.2 Interrupt exception handler

These example interrupt exception handlers use Power Architecture assembly code.

0 108

010

Clock

Interrupt request to processor

Hardware vector enable

Interrupt vector

Interrupt acknowledge

Read INTC_IACKR

Write INTC_EOIR

INTVEC in INTC_IACKR

PRI in INTC_CPR

Peripheral interrupt request 100

0 108

Loading...

Loading...