Nexus Development Interface (NDI) RM0046

902/936 Doc ID 16912 Rev 5

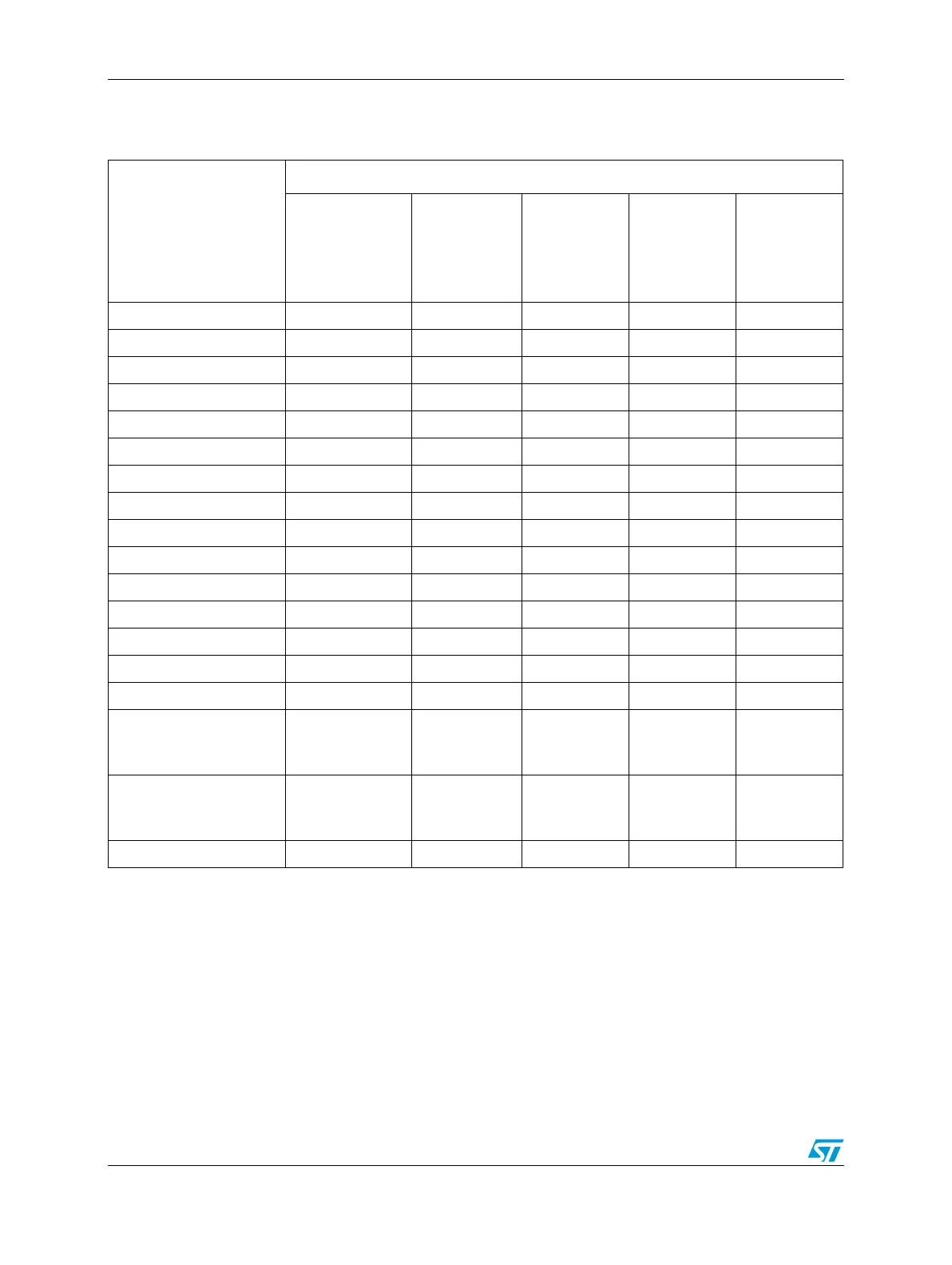

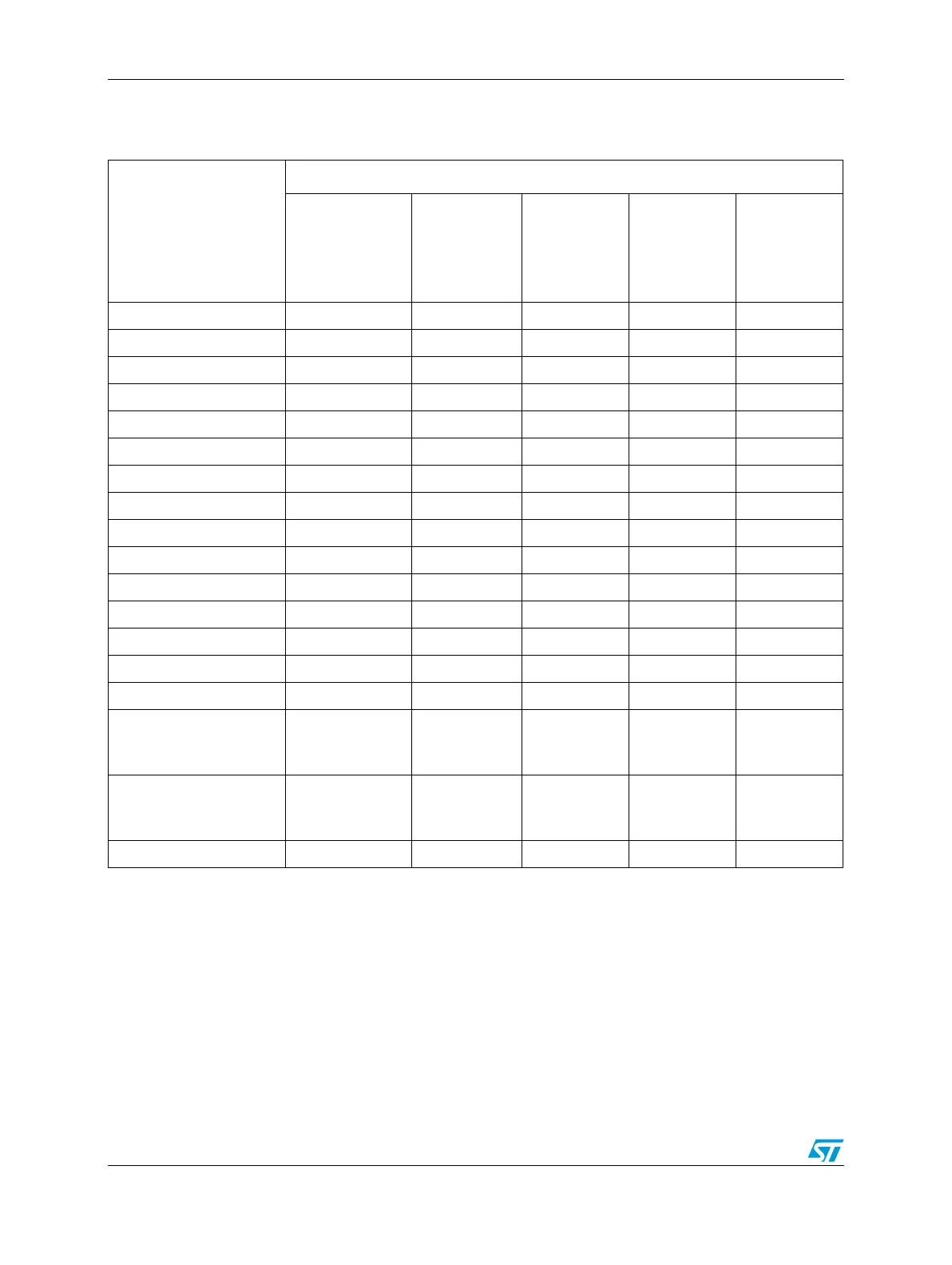

Table 471 provides a list of access requirements for OnCE registers.

Table 471. OnCE Register Access Requirements

Register

Name

Access Requirements

Requires

jd_en_once to

be asserted

Requires

DBCR0

[EDM] = 1

Requires

m_clk active

for Write

Access

Requires

CPU to be

halted

for Read

Access

Requires

CPU to be

halted

for Write

Access

Enable_OnCE N N N N —

Bypass N NNNN

CPUSCR Y Y Y Y Y

DAC1 Y Y Y N

(1)

DAC2 Y Y Y N

(1)

DBCR0

(2)

YYYN

(1)

DBCR1 Y Y Y N

(1)

DBCR2 Y Y Y N

(1)

DBCR4 Y Y Y N

(1)

DBERC0 Y N Y N

(1)

DBSR Y Y Y N

(3) (1)

IAC1–4 Y Y Y N

(1)

JTAG ID

(4)

NN—N—

OCR Y NNNN

OSR

(5)

YN—N—

Cache Debug Access

Control

(CDACNTL)

(6),(7)

YNYYY

Cache Debug Access

Data

(CDADATA)

(6),(7)

YNYYY

External GPRs Y N N N N

1. Writes to these registers while the CPU is running may have unpredictable results due to the pipelined nature of operation,

and the fact that updates are not synchronized to a particular clock, instruction, or bus cycle boundary, therefore it is

strongly recommended to ensure the processor is first placed into debug mode before updates to these registers are

performed.

2. DBCR0

EDM

access only requires jd_en_once asserted.

3. Reads of these registers while the CPU is running may not give data that is self-consistent due to synchronization across

clock domains.

4. Read-only.

5. Read-only, accessed by scanning out IR while jd_en_once is asserted.

6. Not present on Z0Hn2p

7. CPU must be in debug mode with clocks running.

Loading...

Loading...