Cross Triggering Unit (CTU) RM0046

632/936 Doc ID 16912 Rev 5

24.8.11 FIFO DMA control register (FDCR)

Table 327. CLRx (CMS = 1) field descriptions

Field Description

CIR

Command Interrupt Request bit

0 Disabled

1 Enabled

FC

First command bit

0 Not first command

1 First command

CMS

Conversion mode selection

0 Single conversion mode

1 Dual conversion mode

FIFO FIFO for ADC unit A/B

CH_B ADC unit B channel number

CH_A ADC unit A channel number

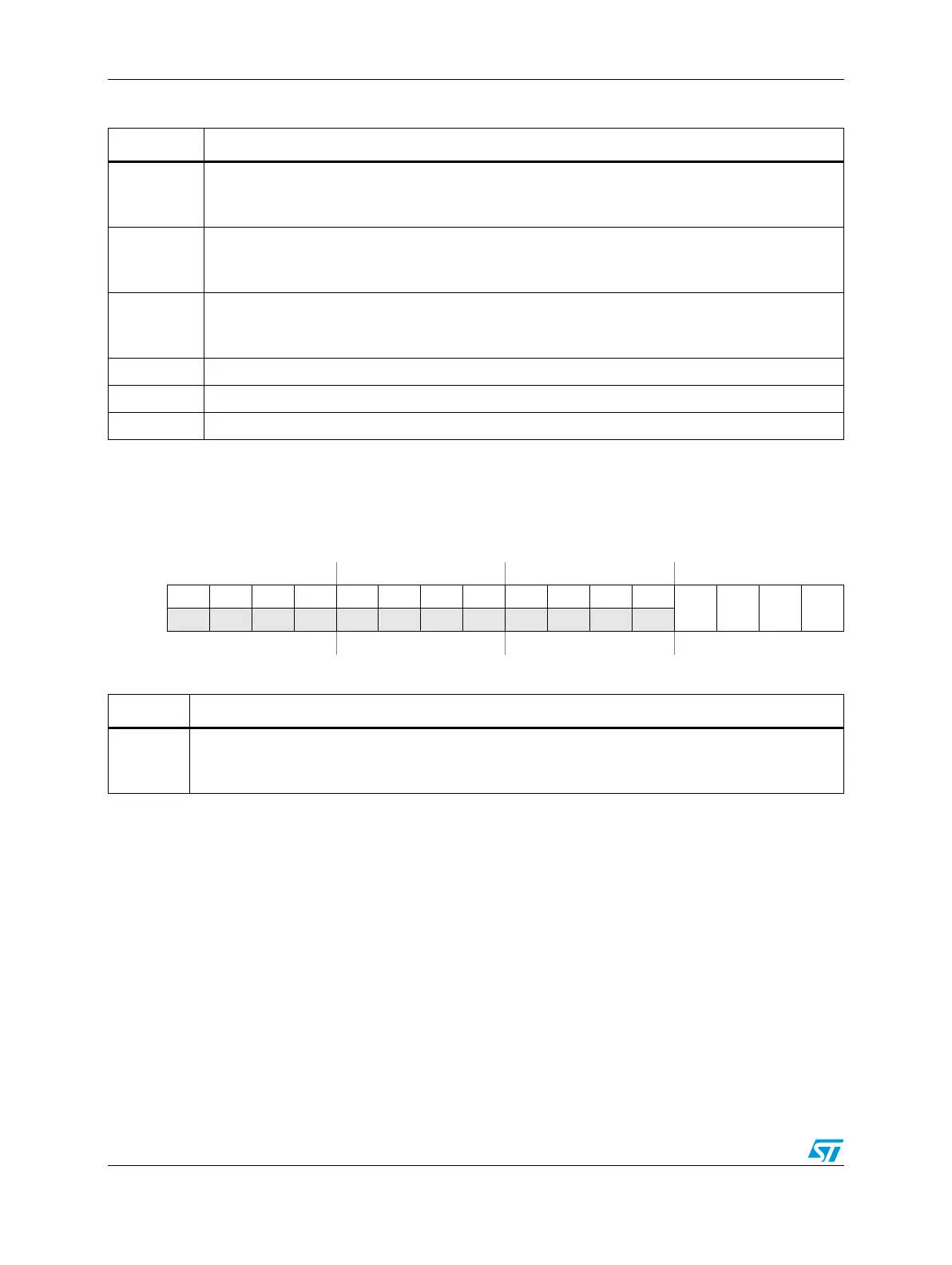

Figure 320. FIFO DMA control register (FDCR)

Address:

Base + 0x006C Access: User read/write

0123456789101112131415

R000000000000

DE3 DE2 DE1 DE0

W

Reset0000000000000000

Table 328. FDCR field descriptions

Name Description

DEx

This bit enables DMA for the FIFOx

0 Disabled

1 Enabled

Loading...

Loading...