FlexPWM RM0046

650/936 Doc ID 16912 Rev 5

25.6.2 Register descriptions

The address of a register is the sum of a base address and an address offset. The base

address is defined at the core level and the address offset is defined at the module level.

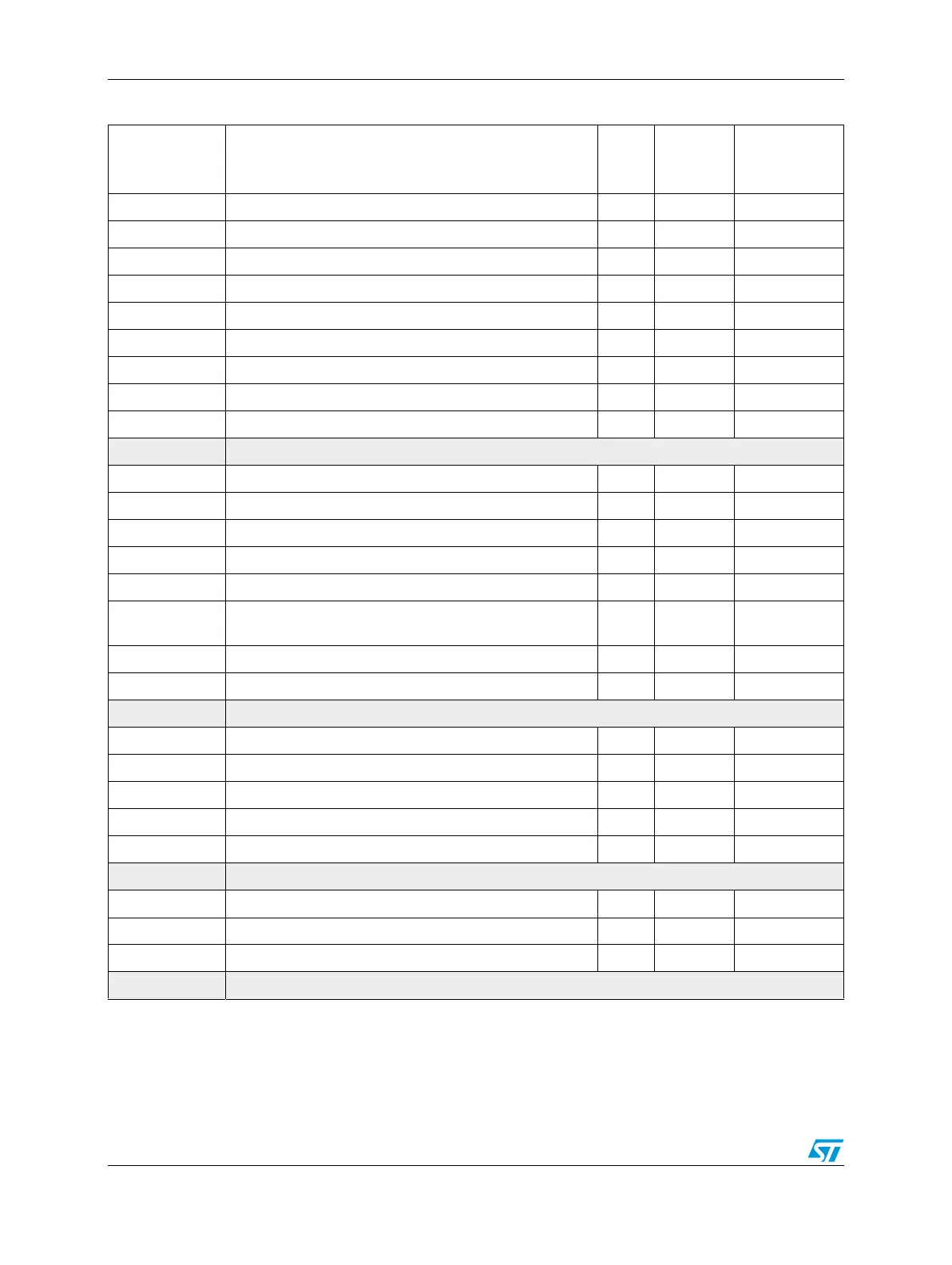

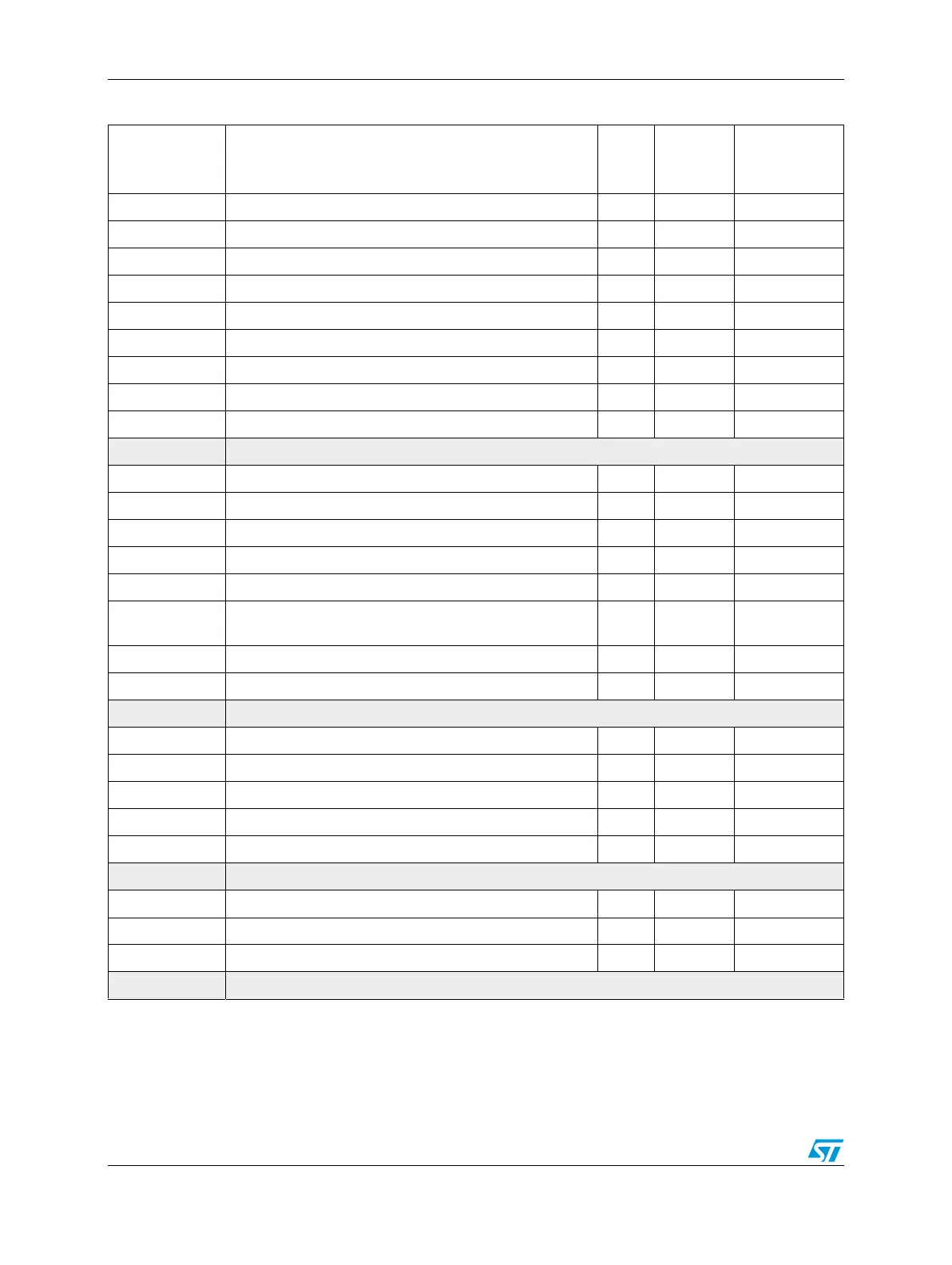

0x00F2 INIT—Initial Count Register (Submodule 3) R/W 0x0000 on page 25-651

0x00F4 CTRL2—Control 2 Register (Submodule 3) R/W 0x0000 on page 25-652

0x00F6 CTRL1—Control 1 Register (Submodule 3) R/W 0x0000 on page 25-654

0x00F8 VAL0—Value Register 0 (Submodule 3) R/W 0x0000 on page 25-656

0x00FA VAL1—Value Register 1 (Submodule 3) R/W 0x0000 on page 25-657

0x00FC VAL2—Value Register 2 (Submodule 3) R/W 0x0000 on page 25-657

0x00FE VAL3—Value Register 3 (Submodule 3) R/W 0x0000 on page 25-658

0x0100 VAL4—Value Register 4 (Submodule 3) R/W 0x0000 on page 25-658

0x0102 VAL5—Value Register 5 (Submodule 3) R/W 0x0000 on page 25-659

0x0104–0x0107 Reserved

0x0108 OCTRL—Output Control Register (Submodule 3) R/W 0x0000 on page 25-659

0x010A STS—Status Register (Submodule 3) R/W 0x0000 on page 25-660

0x010C INTEN—Interrupt Enable Register (Submodule 3) R/W 0x0000 on page 25-661

0x010E DMAEN—DMA Enable Register (Submodule 3) R/W 0x0000 on page 25-662

0x0110 TCTRL—Output Trigger Control Register (Submodule 3) R/W 0x0000 on page 25-663

0x0112

DISMAP—Fault Disable Mapping Register (Submodule

3)

R/W 0xFFFF on page 25-664

0x0114 DTCNT0—Deadtime Count Register 0 (Submodule 3) R/W 0x07FF on page 25-664

0x0116 DTCNT1—Deadtime Count Register 1 (Submodule 3) R/W 0x07FF on page 25-664

0x0118–0x013F Reserved

0x0140 OUTEN—Output Enable Register R/W 0x0000 on page 25-665

0x142 MASK—Output Mask Register R/W 0x0000 on page 25-666

0x0144 SWCOUT—Software Controlled Output Register R/W 0x0000 on page 25-667

0x0146 DTSRCSEL—Deadtime Source Select Register R/W 0x0000 on page 25-668

0x0148 MCTRL—Master Control Register R/W 0x0000 on page 25-670

0x014A Reserved

0x014C FCTRL—Fault Control Register R/W 0x0000 on page 25-671

0x014E FSTS—Fault Status Register R/W 0x0303 on page 25-672

0x0150 FFILT—Fault Filter Register R/W 0x0000 on page 25-673

0x0152–0x3FFF Reserved

Table 342. FlexPWM memory map (continued)

Offset from

FlexPWM_BASE

(0xFFE2_4000)

Register

Access

Reset

value

Location

Loading...

Loading...