RM0046 Enhanced Direct Memory Access (eDMA)

Doc ID 16912 Rev 5 397/936

eDMA Error Register (EDMA_ERL)

The EDMA_ERL provides a bit map for the 16 channels signaling the presence of an error

for each channel. EDMA_ERL maps to channels 15-0.

The eDMA engine signals the occurrence of a error condition by setting the appropriate bit

in this register. The outputs of this register are enabled by the contents of the EDMA_EEIR,

then logically summed across groups of 16 and 32 channels to form several group error

interrupt requests that are then routed to the interrupt controller. During the execution of the

interrupt service routine associated with any DMA errors, it is software’s responsibility to

clear the appropriate bit, negating the error interrupt request. Typically, a write to the

EDMA_CERR in the interrupt service routine is used for this purpose. Recall the normal

DMA channel completion indicators, setting the transfer control descriptor DONE flag and

the possible assertion of an interrupt request, are not affected when an error is detected.

The contents of this register can also be polled and a non-zero value indicates the presence

of a channel error, regardless of the state of the EDMA_EEIR. The EDMA_ESR[VLD] bit is a

logical OR of all bits in this register and it provides a single bit indication of any errors. The

state of any given channel’s error indicators is affected by writes to this register; it is also

affected by writes to the EDMA_CERR. On writes to EDMA_ERL, a 1 in any bit position

clears the corresponding channel’s error status. A 0 in any bit position has no affect on the

corresponding channel’s current error status. The EDMA_CERR is provided so the error

indicator for a single channel can easily be cleared.

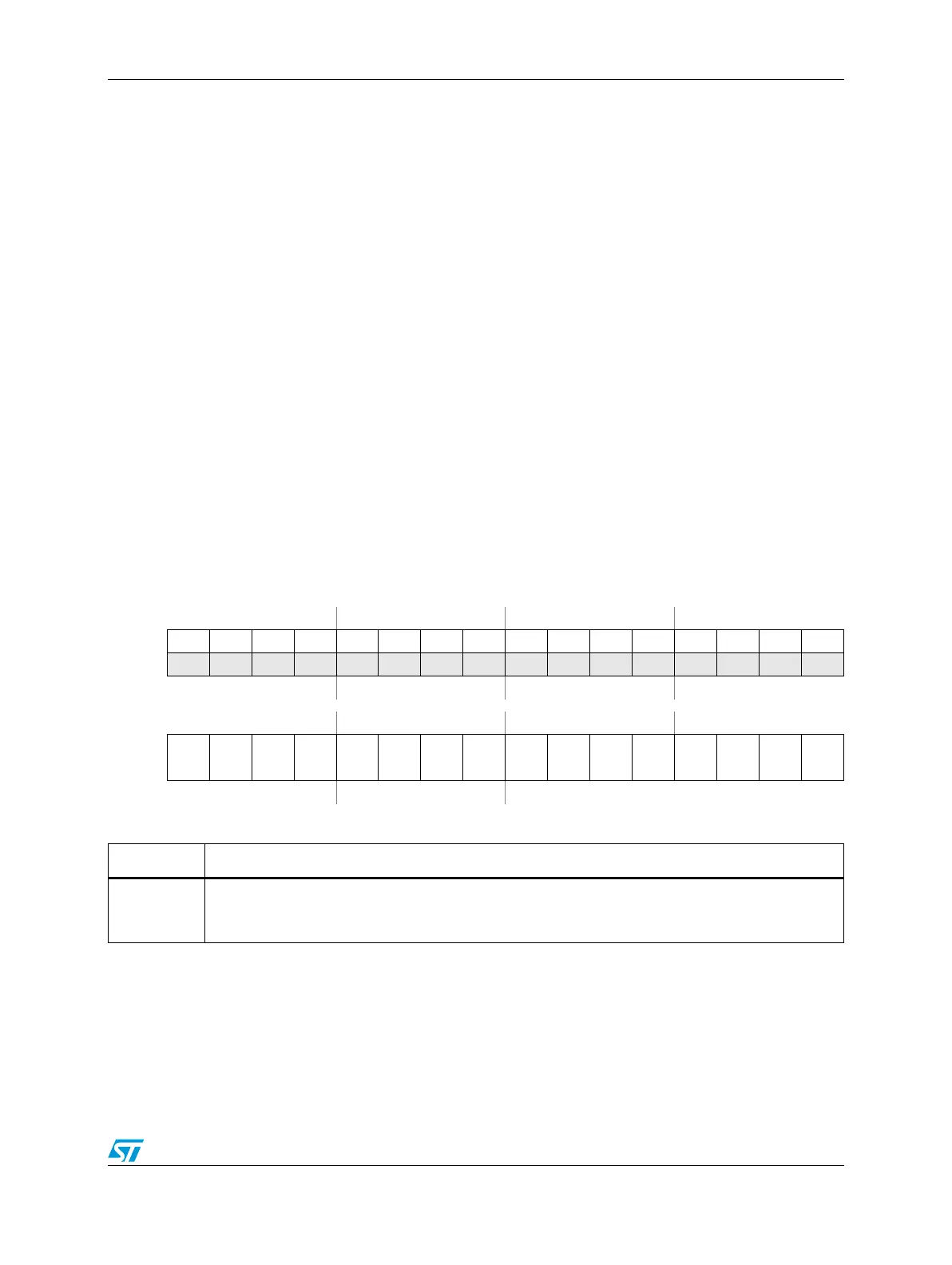

DMA Hardware Request Status (DMAHRSL)

The DMAHRSL registers provide a bit map for the implemented channels 16 to show the

current hardware request status for each channel. DMAHRSL covers channels 31:00.

Hardware request status reflects the current state of the registered and qualified (via the

DMAERQ field) ipd_req lines as seen by the eDMA’s arbitration logic. This view into the

hardware request signals may be used for debug purposes.

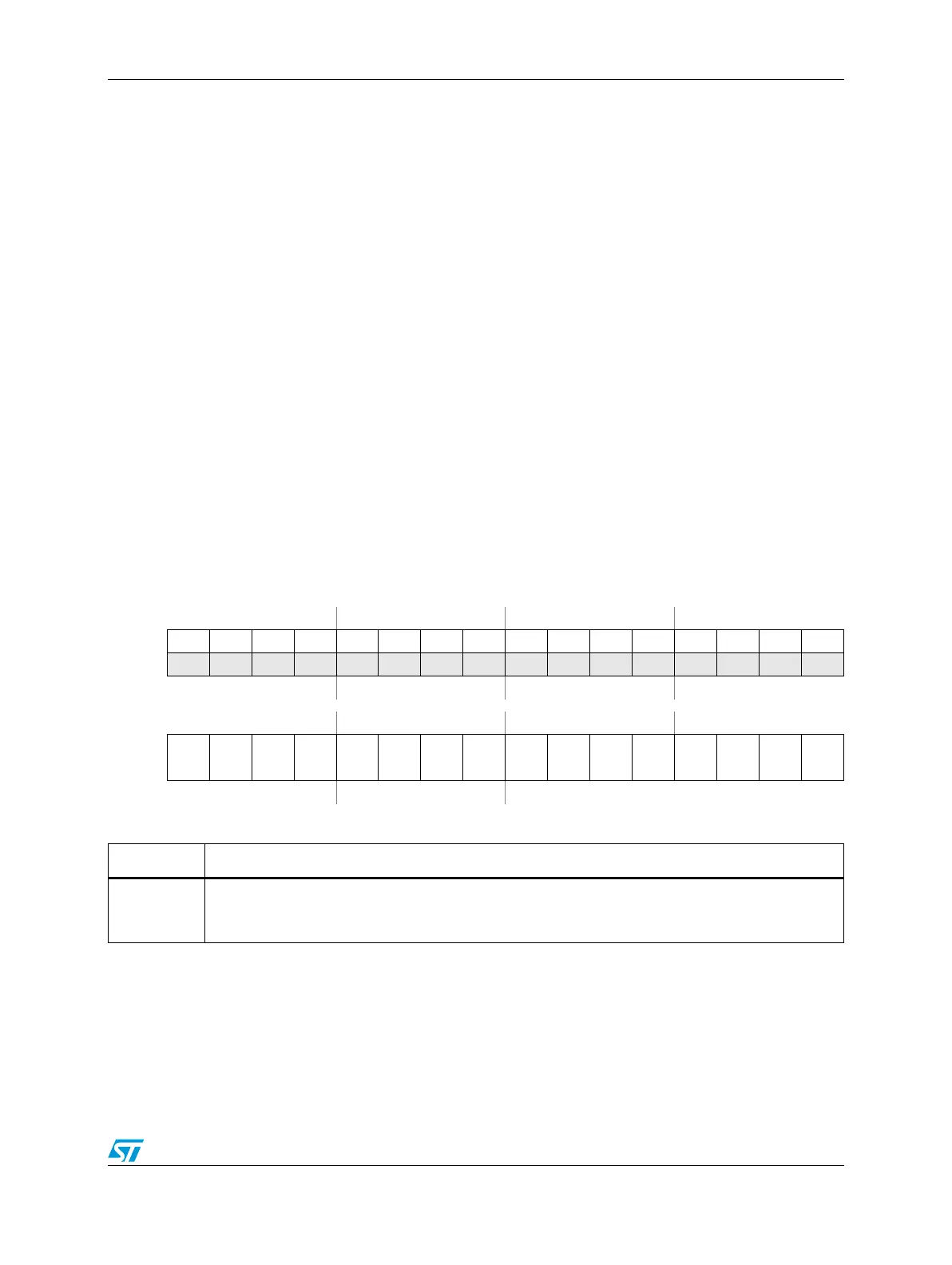

Figure 190. eDMA Error Low Register (EDMA_ERL)

Address:

Base + 0x002C Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

ERR

15

ERR

14

ERR

13

ERR

12

ERR

11

ERR

10

ERR

09

ERR

08

ERR

07

ERR

06

ERR

05

ERR

04

ERR

03

ERR

02

ERR

01

ERR

00

W

Reset0000000000000000

Table 189. EDMA_ERL field descriptions

Field Description

16–31

ERRn

eDMA Error n.

0 An error in channel n has not occurred.

1 An error in channel n has occurred.

Loading...

Loading...