Interrupt Controller (INTC) RM0046

220/936 Doc ID 16912 Rev 5

9.6 Functional description

The functional description involves the areas of interrupt request sources, priority

management, and handshaking with the processor.

Note: The INTC has no spurious vector support. Therefore, if an asserted peripheral or software

settable interrupt request, whose PRIn value in INTC_PSR0–INTC_PSR221 is higher than

the PRI value in INTC_CPR, negates before the interrupt request to the processor for that

peripheral or software settable interrupt request is acknowledged, the interrupt request to

the processor still can assert or will remain asserted for that peripheral or software settable

interrupt request. In this case, the interrupt vector will correspond to that peripheral or

software settable interrupt request. Also, the PRI value in the INTC_CPR will be updated

with the corresponding PRIn value in INTC_PSRn. Furthermore, clearing the peripheral

interrupt request’s enable bit in the peripheral or, alternatively, setting its mask bit has the

same consequences as clearing its flag bit. Setting its enable bit or clearing its mask bit

while its flag bit is asserted has the same effect on the INTC as an interrupt event setting the

flag bit.

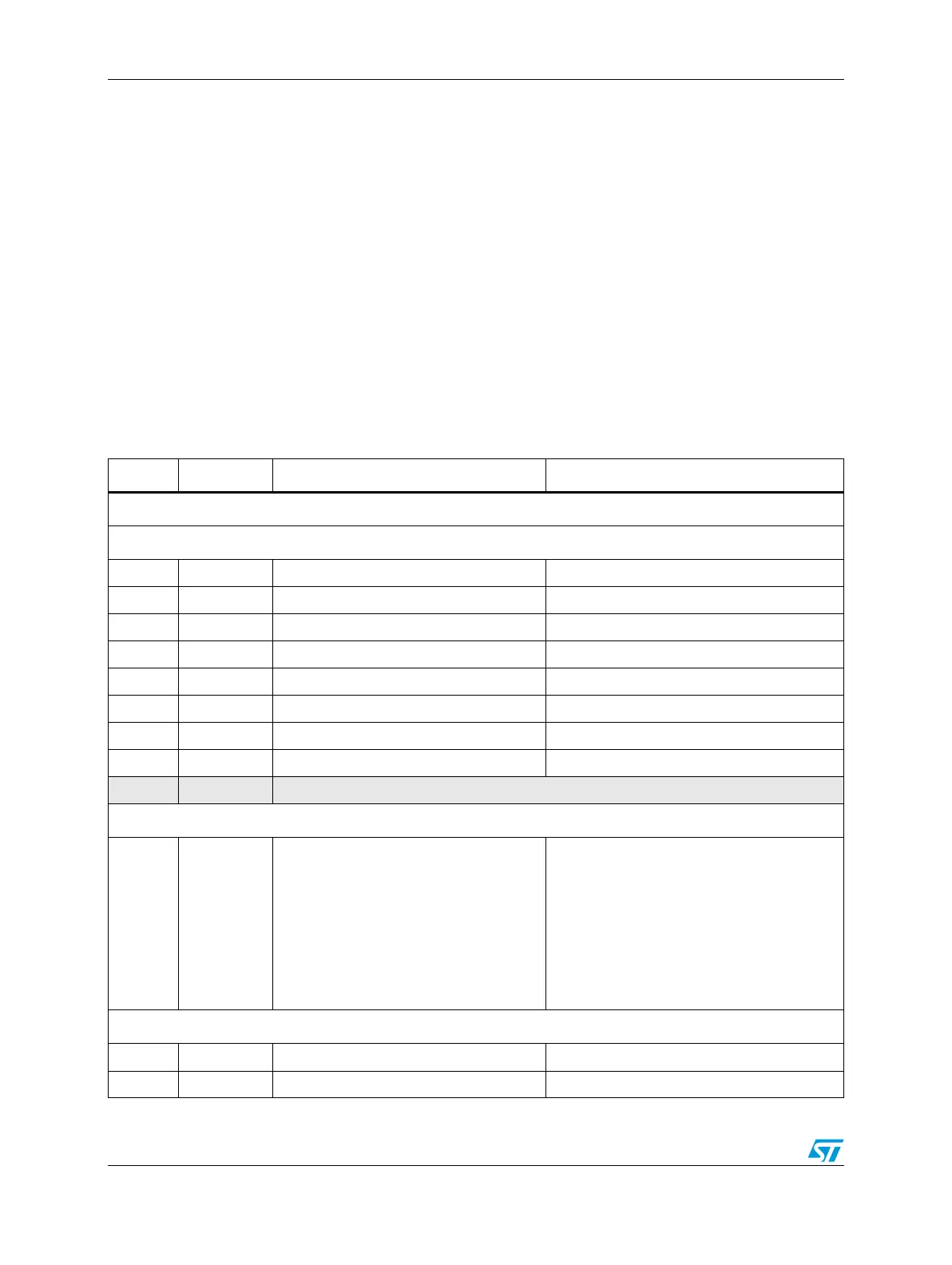

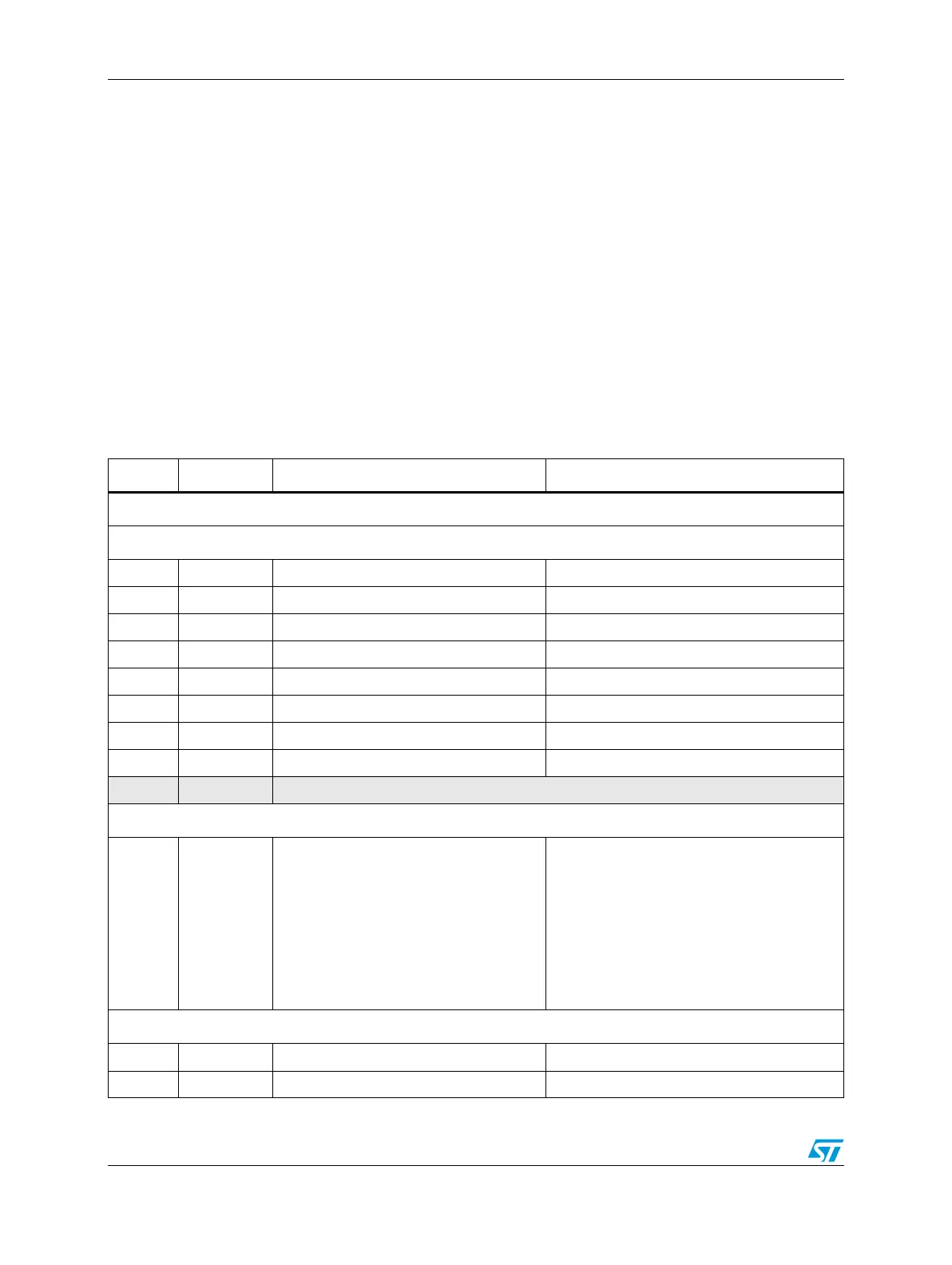

Table 75. Interrupt vector table

IRQ # Offset Interrupt Module

On-Platform Peripherals

Software Interrupts

0 0x0800 Software configurable flag 0 Software

1 0x0804 Software configurable flag 1 Software

2 0x0808 Software configurable flag 2 Software

3 0x080C Software configurable flag 3 Software

4 0x0810 Software configurable flag 4 Software

5 0x0814 Software configurable flag 5 Software

6 0x0818 Software configurable flag 6 Software

7 0x081C Software configurable flag 7 Software

8 0x0820 Reserved

ECSM

9

0x0824

Platform Flash Bank 0 Abort |

Platform Flash Bank 0 Stall |

Platform Flash Bank 1 Abort |

Platform Flash Bank 1 Stall |

Platform Flash Bank 2 Abort |

Platform Flash Bank 2 Stall |

Platform Flash Bank 3 Abort |

Platform Flash Bank 3 Stall

ECSM

DMA2x

10 0x0828 Combined Error DMA2x

11 0x082C Channel 0 DMA2x

Loading...

Loading...