Clock Description RM0046

100/936 Doc ID 16912 Rev 5

4.8 Frequency Modulated Phase Locked Loop (FMPLL)

4.8.1 Introduction

This section describes the features and functions of the FMPLL module implemented in

SPC560P40/34.

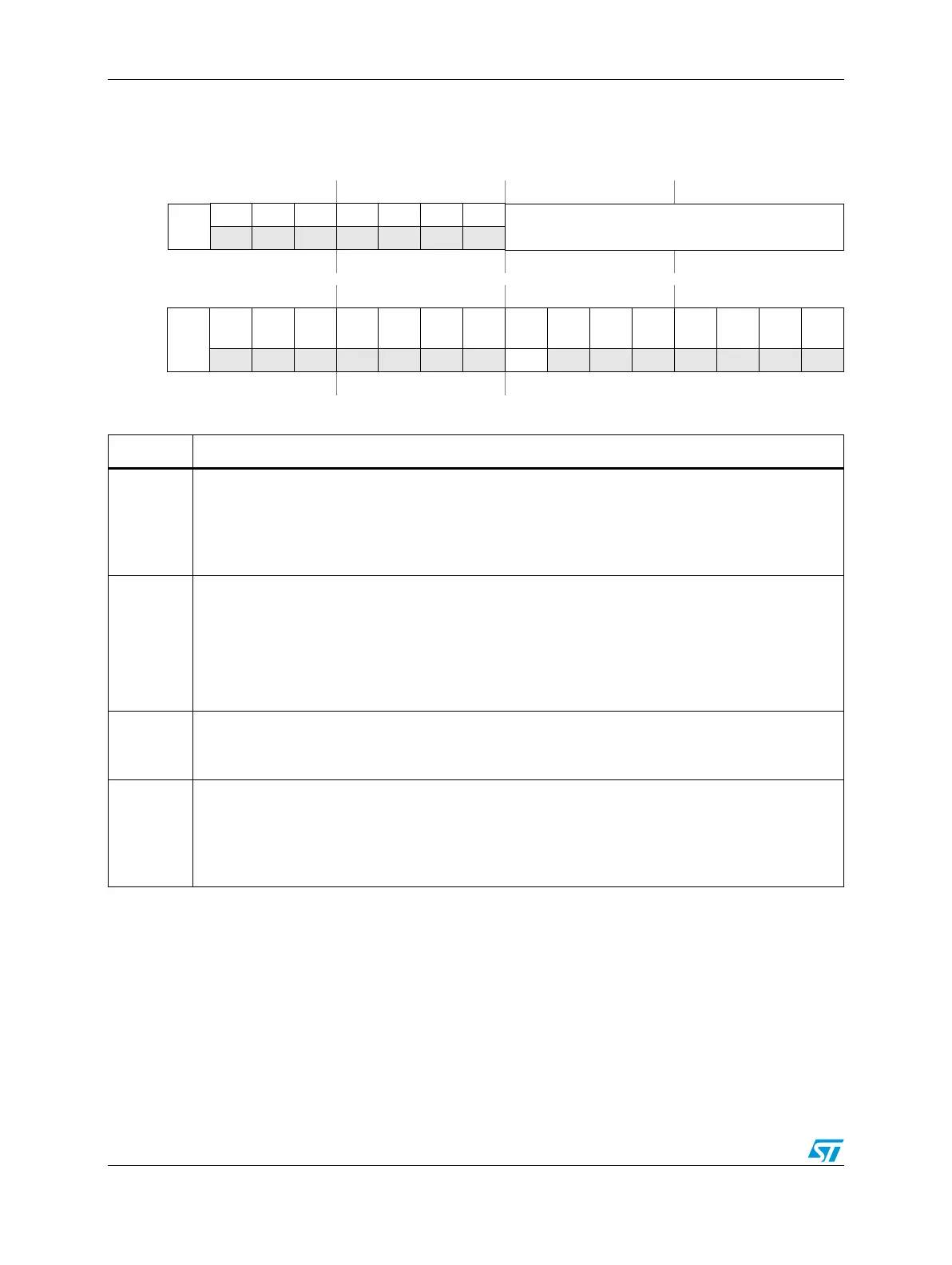

Figure 13. Crystal Oscillator Control register (OSC_CTL)

Address:

0xC3FE_0000

(Base + 0x0000)

Access: Supervisor read/write; User read-

only

0123456789101112131415

R

OSC

BYP

0000000

EOCV[7:0]

W

Reset0000000010000000

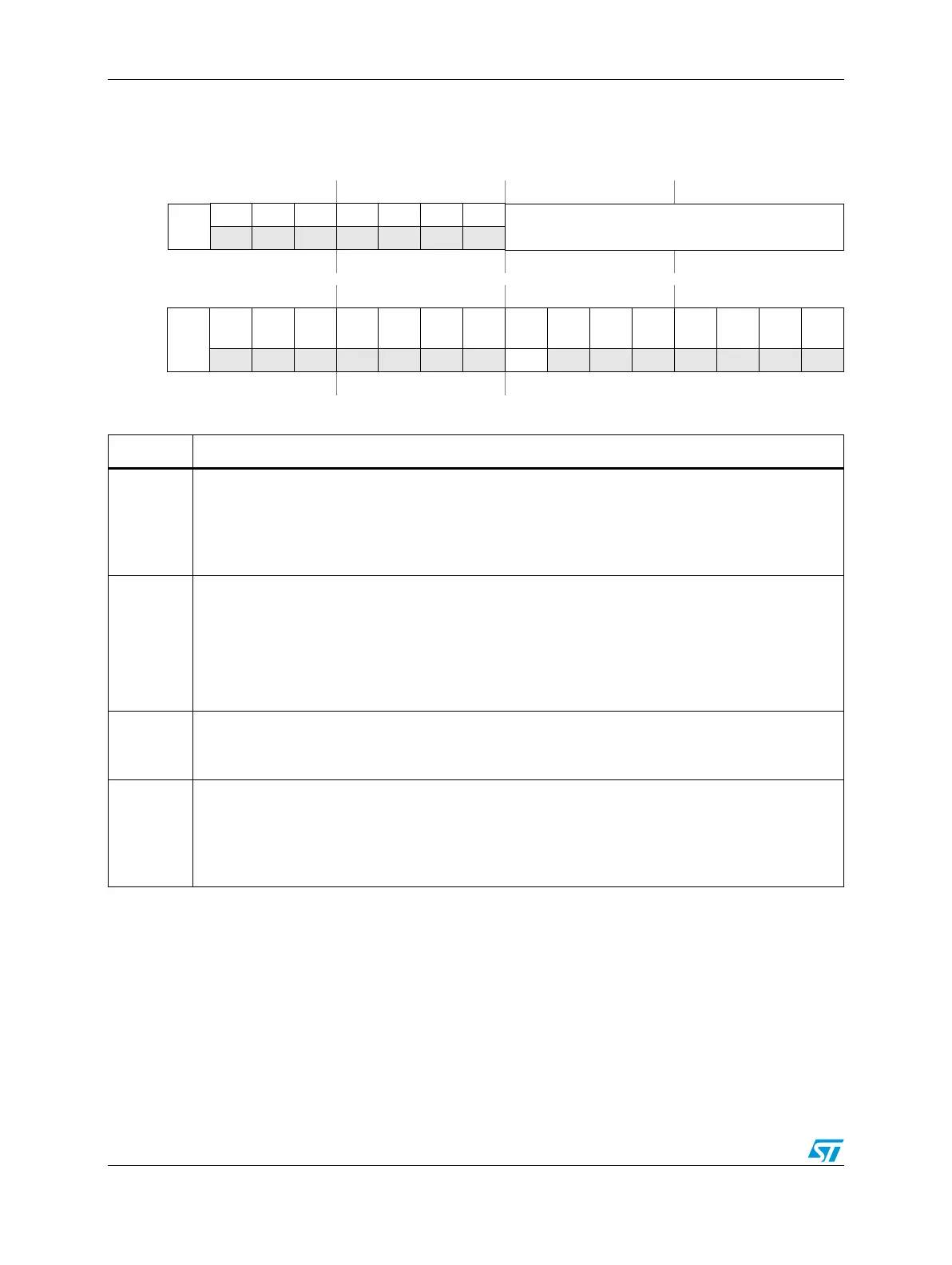

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

M_

OSC

0000000

I_

OSC

0000000

W

w1c

Reset0000000000000000

Table 11. OSC_CTL field descriptions

Field Description

OSCBYP

Crystal Oscillator bypass

This bit specifies whether the oscillator should be bypassed or not. Software can only set this bit.

System reset is needed to reset this bit.

0: Oscillator output is used as root clock.

1: EXTAL is used as root clock.

EOCV[7:0]

End of Count Value

These bits specify the end of count value to be used for comparison by the oscillator stabilization

counter OSCCNT after reset or whenever it is switched on from the off state. This counting period

ensures that external oscillator clock signal is stable before it can be selected by the system. When

oscillator counter reaches the value EOCV[7:0]*512, oscillator available interrupt request is

generated. The reset value of this field depends on the device specification. The OSCCNT counter

will be kept under reset if oscillator bypass mode is selected.

M_OSC

Crystal oscillator clock interrupt mask

0: Crystal oscillator clock interrupt masked

1: Crystal oscillator clock interrupt enabled

I_OSC

Crystal oscillator clock interrupt

This bit is set by hardware when OSCCNT counter reaches the count value EOCV[7:0]*512. It is

cleared by software by writing 1.

0: No oscillator clock interrupt occurred

1: Oscillator clock interrupt pending

Loading...

Loading...