RM0046 Nexus Development Interface (NDI)

Doc ID 16912 Rev 5 897/936

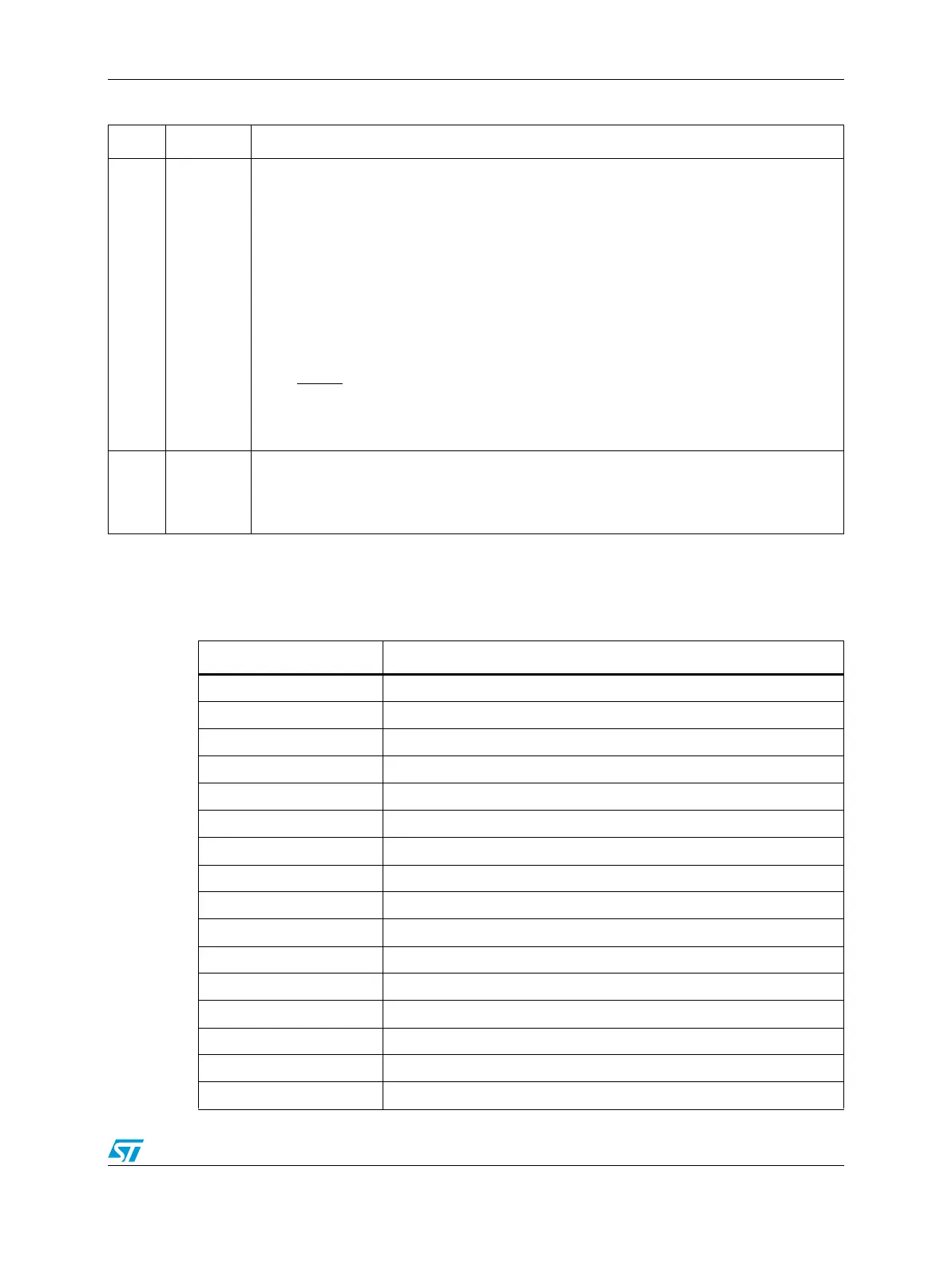

Table 469 indicates the e200z0h OnCE register addresses.

2EX

Exit Command Bit

0 – Remain in debug mode

1 – Leave debug mode

If the EX bit is set, the processor will leave the debug mode and resume normal operation

until another debug request is generated. The Exit command is executed only if the Go

command is issued, and the operation is a read/write to CPUSCR or a read/write to “No

Register Selected”. Otherwise the EX bit is ignored.

The processor will leave the debug mode after the TAP controller Update-DR state is

entered. Note that if the DR bit in the OnCE control register is set or remains set, or if a

hardware-owned bit in DBSR is set and DBCR0

EDM

=1 (external debug mode is enabled), or

if another debug request source is asserted, then the processor may return to the debug

mode without

execution of an instruction, even though the EX bit was set.

Note that asynchronous interrupts are blocked on a GO+Exit operation until the first

instruction to be executed begins execution.

3:9 RS

Register Select

The Register Select bits define which register is source (destination) for the read (write)

operation. Ta bl e 4 6 9 indicates the e200z0h OnCE register addresses. Attempted writes to

read-only registers are ignored.

Table 468. OnCE Command Register Bit Definitions (continued)

Bit(s) Name Description

Table 469. e200z0h OnCE Register Addressing

RS[0:6] Register Selected

000 0000 Reserved

000 0001 Reserved

000 0010 JTAG ID (read-only)

000 0011 – 000 1111 Reserved

001 0000 CPU Scan Register (CPUSCR)

001 0001 No Register Selected (Bypass)

001 0010 OnCE Control Register (OCR)

001 0011 Reserved

001 0100 – 001 1111 Reserved

010 0000 Instruction Address Compare 1 (IAC1)

010 0001 Instruction Address Compare 2 (IAC2)

010 0010 Instruction Address Compare 3 (IAC3)

010 0011 Instruction Address Compare 4 (IAC4)

010 0100 Data Address Compare 1 (DAC1)

010 0101 Data Address Compare 2 (DAC2)

010 0110 Data Value Compare 1 (DVC1)

Loading...

Loading...