Error Correction Status Module (ECSM) RM0046

304/936 Doc ID 16912 Rev 5

RAM ECC Master Number Register (REMR)

The REMR is an 8-bit register in which the 4-bit field REMR[0:3] is used for capturing the

XBAR bus master number of the last properly enabled ECC event in the RAM memory.

Depending on the state of the ECC Configuration Register, an ECC event in the RAM

causes the address, attributes and data associated with the access to be loaded into the

REAR, RESR, REMR, REAT and REDR registers, and the appropriate flag (R1BC or

RNCE) in the ECC Status Register to be asserted.

This register can only be read from the IPS programming model; any attempted write is

ignored.

RAM ECC Attributes (REAT) register

The REAT is an 8-bit register for capturing the XBAR bus master attributes of the last

properly enabled ECC event in the RAM memory. Depending on the state of the ECC

Configuration Register, an ECC event in the RAM causes the address, attributes and data

associated with the access to be loaded into the REAR, RESR, REMR, REAT and REDR

registers, and the appropriate flag (R1BC or RNCE) in the ECC Status Register to be

asserted.

This register can only be read from the IPS programming model; any attempted write is

ignored.

0x4C DATA ODD BANK[0]

0x03,0x05........0x4D Multiple bit error

> 0x4D Multiple bit error

Table 130. RAM syndrome mapping for single-bit correctable errors (continued)

RESR[7:0] Data Bit in Error

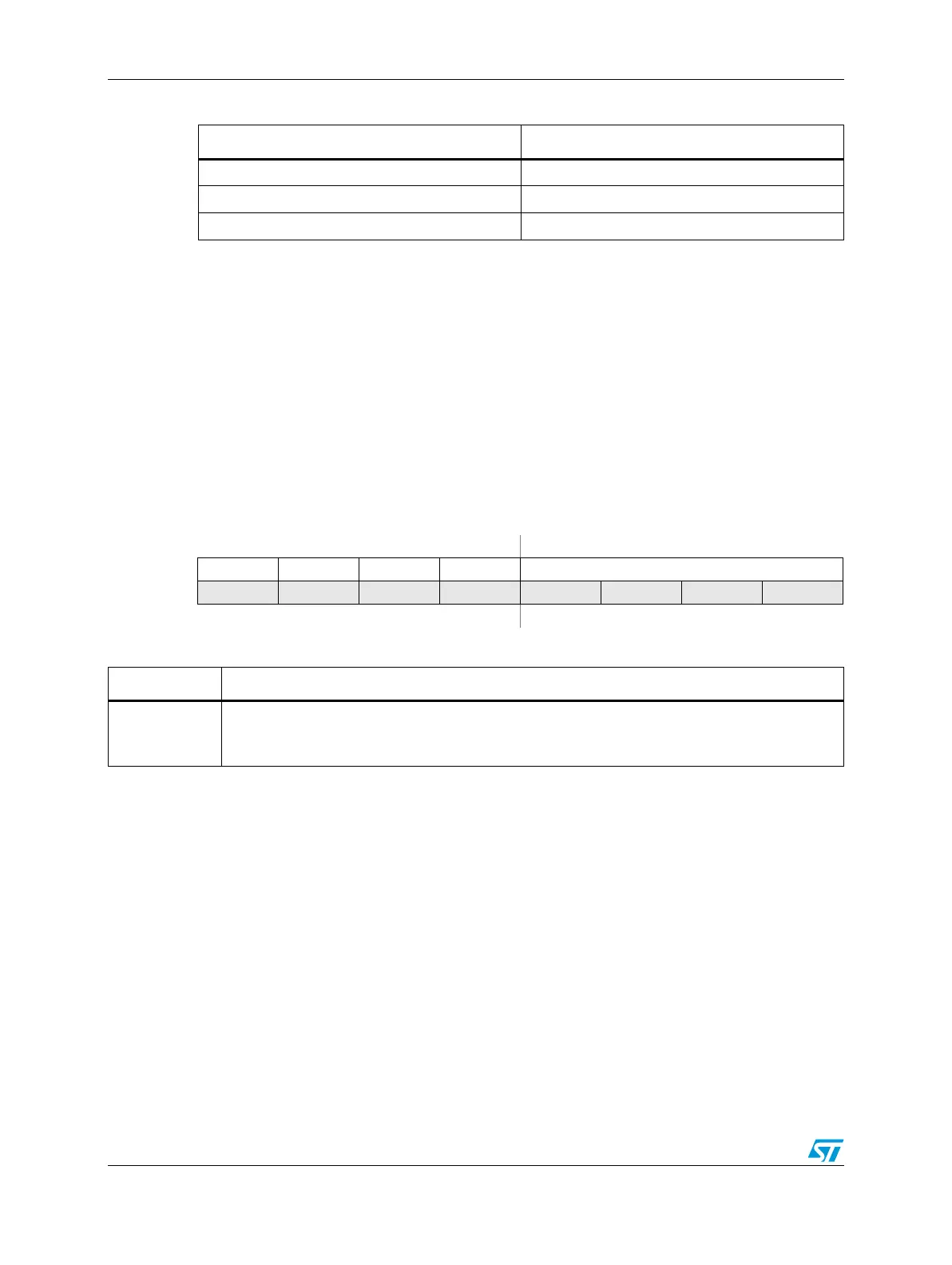

Figure 140. RAM ECC Master Number register (REMR)

Address: Base + 0x0066 Access: User read-only

01234567

R 0 0 0 0 REMR[3:0]

W

Reset 0 0 0 0 — — — —

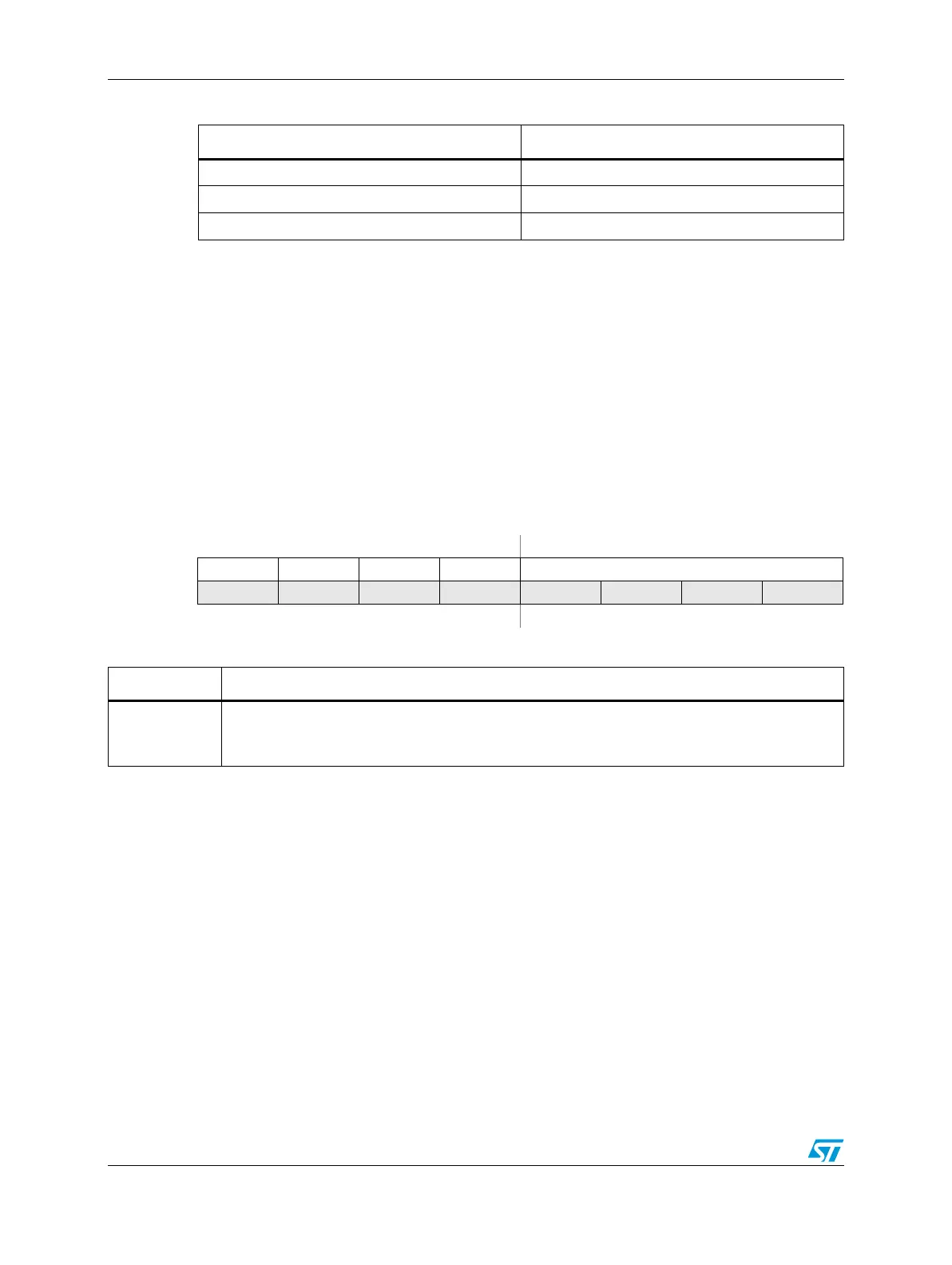

Table 131. REMR field descriptions

Name Description

4-7

REMR[3:0]

RAM ECC Master Number Register

This 4-bit field contains the XBAR bus master number of the faulting access of the last properly

enabled RAM ECC event.

Loading...

Loading...