Mode Entry Module (MC_ME) RM0046

152/936 Doc ID 16912 Rev 5

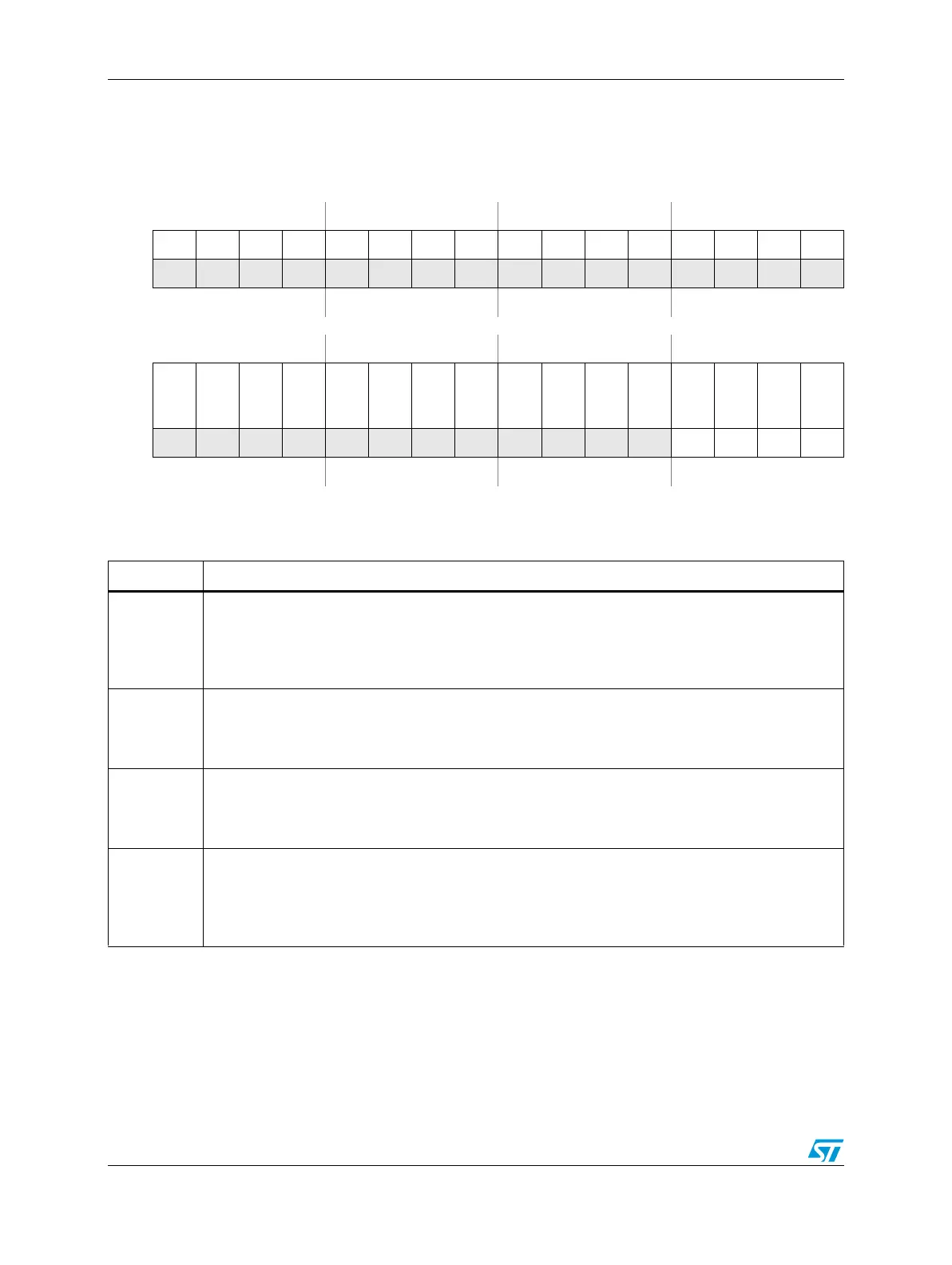

Interrupt Status Register (ME_IS)

This register provides the current interrupt status.

Figure 46. Interrupt Status Register (ME_IS)

Address 0xC3FD_C00C Access: User read, Supervisor read/write, Test read/write

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R000000000000

I_ICONF

I_IMODE

I_SAFE

I_MTC

W w1c w1c w1c w1c

Reset0000000000000000

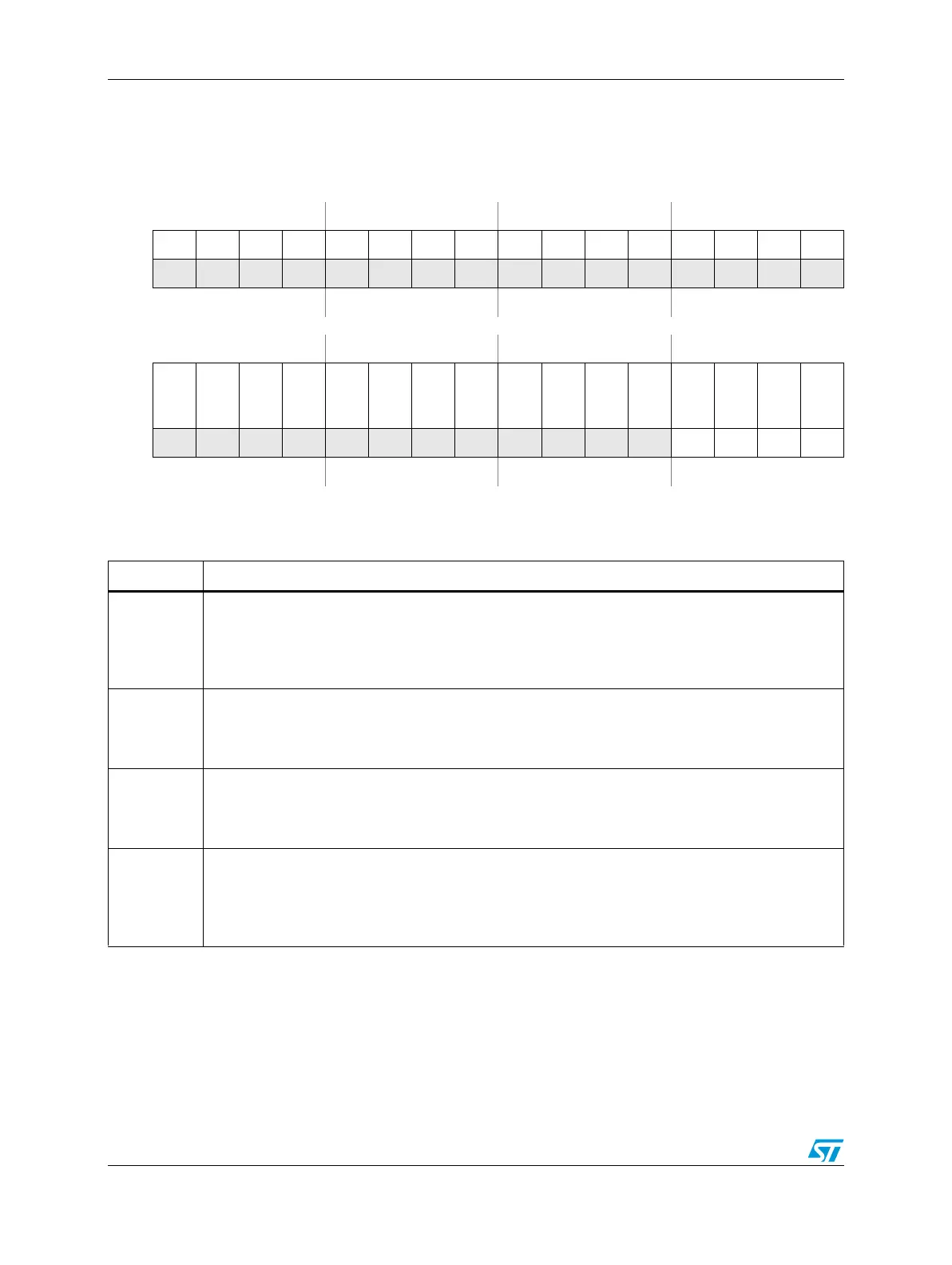

Table 42. Interrupt Status Register (ME_IS) Field Descriptions

Field Description

I_ICONF

Invalid mode configuration interrupt — This bit is set whenever a write operation to

ME_<mode>_MC registers with invalid mode configuration is attempted. It is cleared by writing a ‘1’

to this bit.

0 No invalid mode configuration interrupt occurred

1 Invalid mode configuration interrupt is pending

I_IMODE

Invalid mode interrupt — This bit is set whenever an invalid mode transition is requested. It is

cleared by writing a ‘1’ to this bit.

0 No invalid mode interrupt occurred

1 Invalid mode interrupt is pending

I_SAFE

SAFE mode interrupt — This bit is set whenever the device enters SAFE mode on hardware

requests generated in the system. It is cleared by writing a ‘1’ to this bit.

0 No SAFE mode interrupt occurred

1 SAFE mode interrupt is pending

I_MTC

Mode transition complete interrupt — This bit is set whenever the mode transition process

completes (S_MTRANS transits from 1 to 0). It is cleared by writing a ‘1’ to this bit. This mode

transition interrupt bit will not be set while entering low-power modes HALT0, or STOP0.

0 No mode transition complete interrupt occurred

1 Mode transition complete interrupt is pending

Loading...

Loading...