RM0046 Flash Memory

Doc ID 16912 Rev 5 349/936

Secondary Low/Mid Address Space Block Locking register (SLL)

The Secondary Low/Mid Address Space Block Locking register provides an alternative

means to protect blocks from being modified. These bits, along with bits in the LML register,

determine if the block is locked from program or Erase. An “OR” of LML and SLL determine

the final lock status. Identical SLL registers are provided in the code Flash and the data

Flash blocks.

In the code Flash module, the SLL register has a related Non-Volatile Secondary Low/Mid

Address Space Block Locking register (NVSLL) located in TestFlash that contains the

default reset value for SLL. The reset value is 0x00XX_XXXX, initially determined by

NVSLL.

The NVSLL register is read during the reset phase of the Flash module and loaded into the

SLL.

Non-Volatile Secondary Low/Mid Address Space Block Locking register

(NVSLL)

The NVSLL register is a 64-bit register, the 32 most significant bits of which (bits 63:32) are

“don’t care” bits that are eventually used to manage ECC codes. Identical NVSLL registers

are provided in the code Flash and the data Flash blocks.

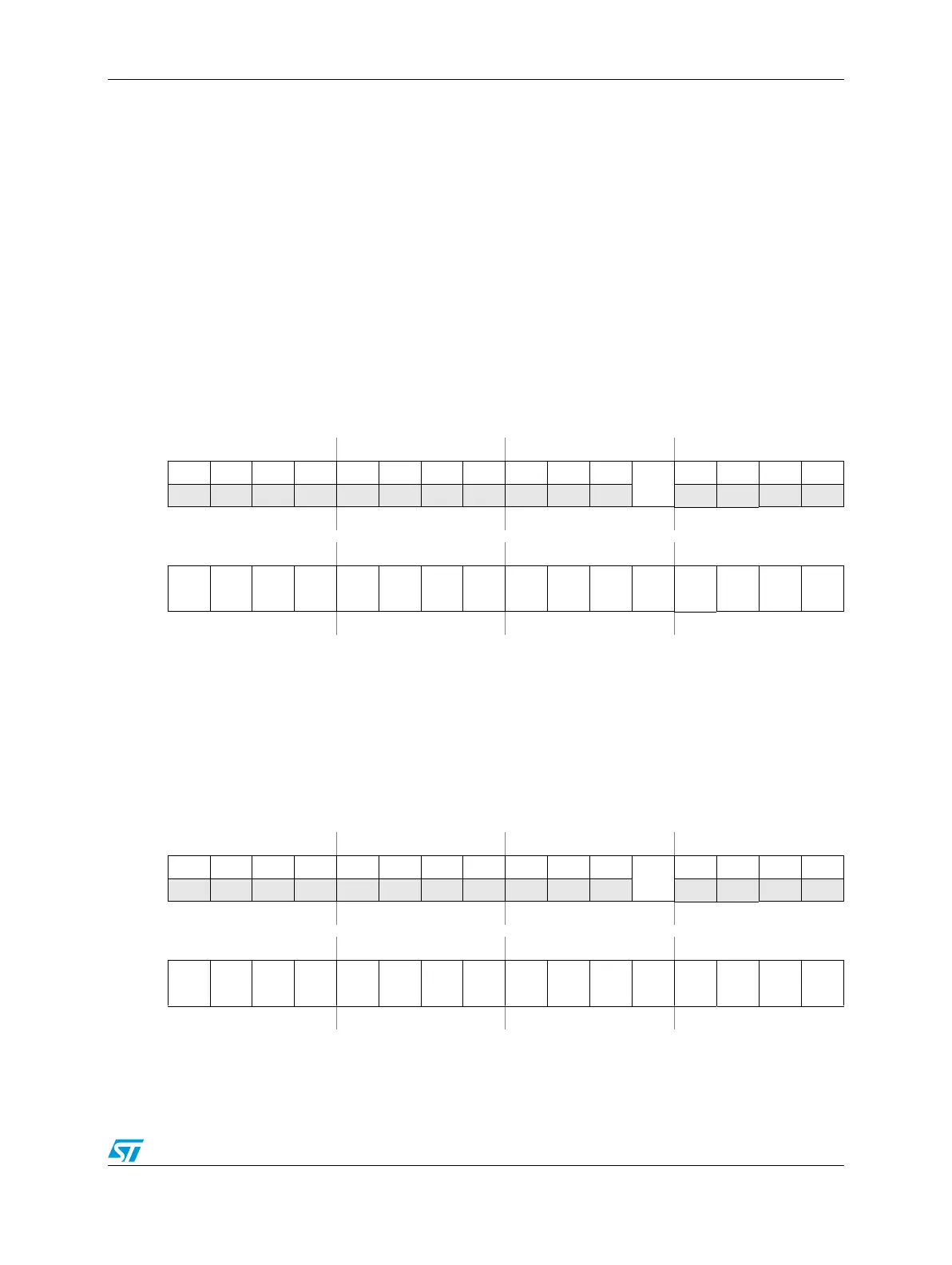

Figure 156. Secondary Low/mid address space block Locking reg (SLL)

Address:

Base + 0x000C Access: User read/write

0123456789101112131415

RSLE0000000 000

STS

LK

0 0 0 0

W

Reset00000000000x00xx

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

SLK

15

SLK

14

SLK

13

SLK

12

SLK

11

SLK

10

SLK

9

SLK

8

SLK

7

SLK

6

SLK

5

SLK

4

SLK

3

SLK

2

SLK

1

SLK

0

W

Resetxxxxxxxxxxxxxxxx

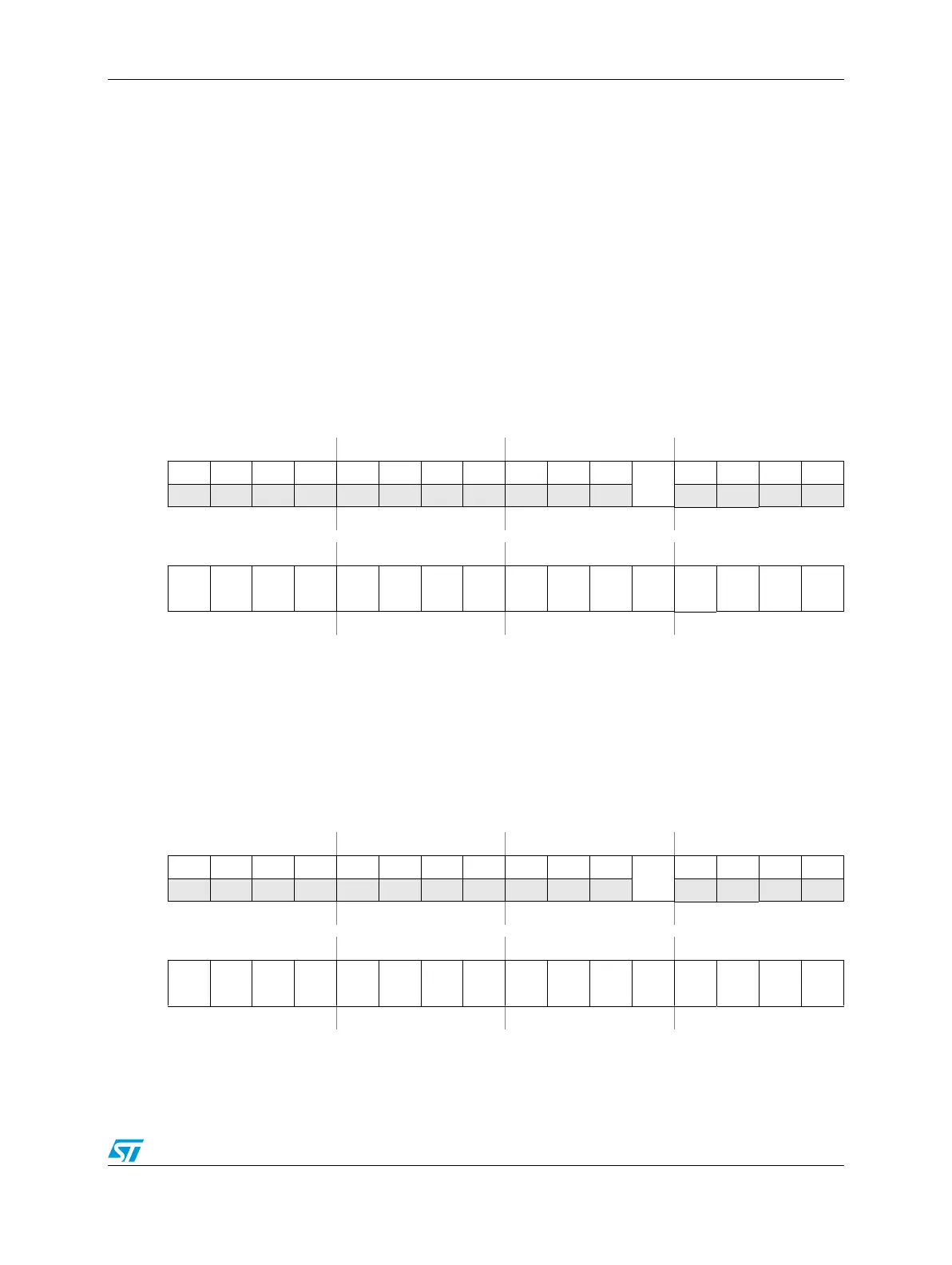

Figure 157. Non-Volatile Secondary Low/Mid Address Space Block Locking register (NVSLL)

Address:

Base + 0x40_3DF8 Access: User read/write

0123456789101112131415

R00000000 000

STS

LK

0 0 0 0

W

Reset00000000000x00xx

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

SLK

15

SLK

14

SLK

13

SLK

12

SLK

11

SLK

10

SLK

9

SLK

8

SLK

7

SLK

6

SLK

5

SLK

4

SLK

3

SLK

2

SLK

1

SLK

0

W

Resetxxxxxxxxxxxxxxxx

Loading...

Loading...