FlexCAN RM0046

554/936 Doc ID 16912 Rev 5

Most bits in this register are read only, except TWRN_INT, RWRN_INT, BOFF_INT, and

ERR_INT, that are interrupt flags that can be cleared by writing 1 to them (writing 0 has no

effect). See Section 22.4.10, “Interrupts for more details.

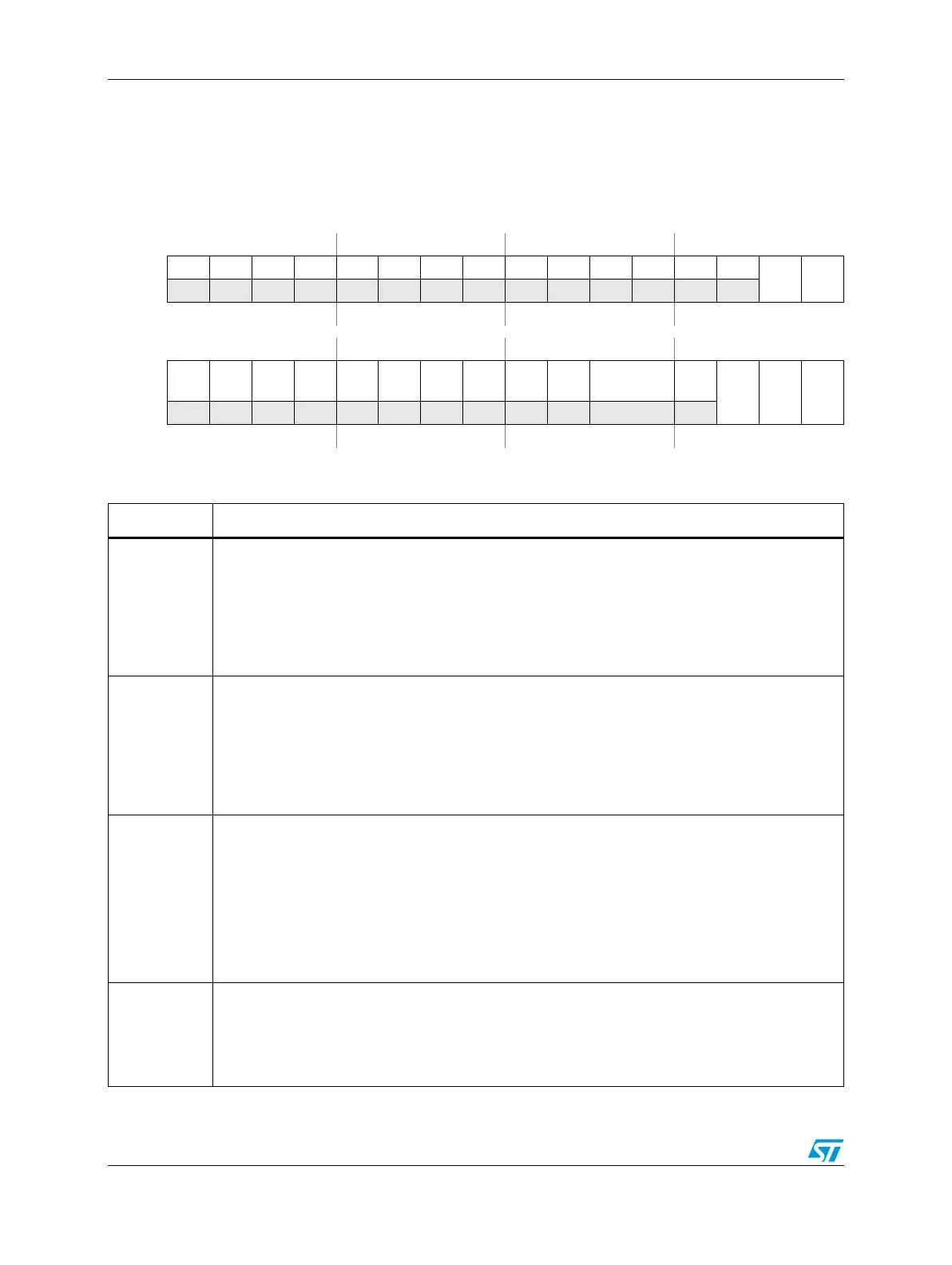

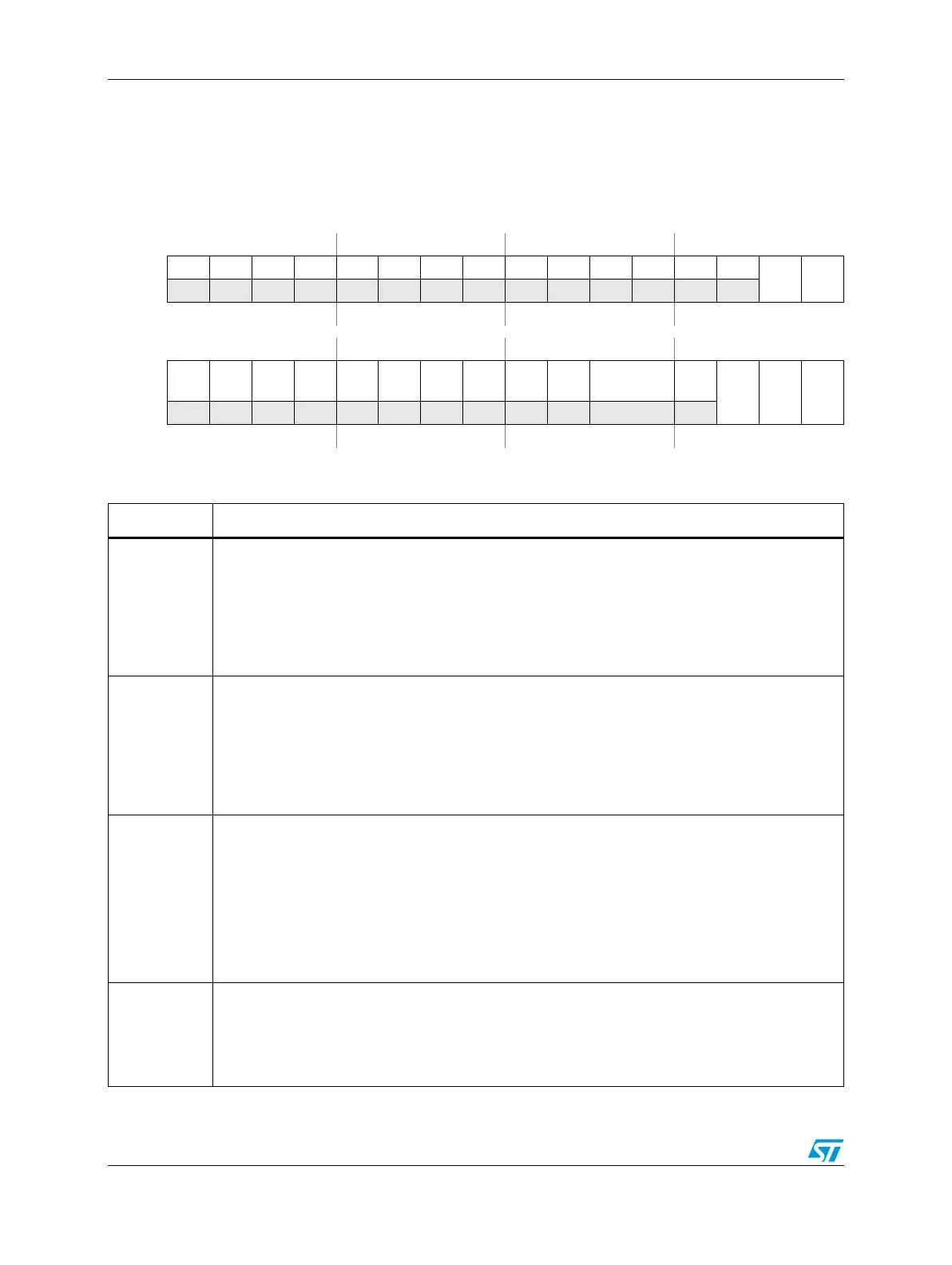

Figure 272. Error and Status Register (ESR)

Address:

Base + 0x0020 Access: User read/write

0123456789101112131415

R00000000 00000 0

TWR

N_INT

RWR

N_INT

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

BIT1_

ERR

BIT0_

ERR

ACK_

ERR

CRC_

ERR

FRM_

ERR

STF_

ERR

TX_

WRN

RX_

WRN

IDLE

TXR

X

FLT_CONF 0

BOFF

_INT

ERR_

INT

WAK_

INT

W

Reset0000000000000000

Table 280. Error and Status Register (ESR) field description

Field Description

14

TWRN_INT

Tx Warning Interrupt Flag

If the WRN_EN bit in MCR is asserted, the TWRN_INT bit is set when the TX_WRN flag transition

from 0 to 1, meaning that the Tx error counter reached 96. If the corresponding mask bit in the

Control Register (TWRN_MSK) is set, an interrupt is generated to the CPU. This bit is cleared by

writing it to 1. Writing 0 has no effect.

0 No such occurrence.

1 The Tx error counter transitioned from < 96 to 96.

15

RWRN_INT

Rx Warning Interrupt Flag

If the WRN_EN bit in MCR is asserted, the RWRN_INT bit is set when the RX_WRN flag transition

from 0 to 1, meaning that the Rx error counters reached 96. If the corresponding mask bit in the

Control Register (RWRN_MSK) is set, an interrupt is generated to the CPU. This bit is cleared by

writing it to 1. Writing 0 has no effect.

0 No such occurrence.

1 The Rx error counter transitioned from < 96 to 96.

16

BIT1_ERR

Bit1 Error

This bit indicates when an inconsistency occurs between the transmitted and the received bit in a

message.

0 No such occurrence.

1 At least one bit sent as recessive is received as dominant.

Note: This bit is not set by a transmitter in case of arbitration field or ACK slot, or in case of

a node sending a passive error flag that detects dominant bits.

17

BIT0_ERR

Bit0 Error

This bit indicates when an inconsistency occurs between the transmitted and the received bit in a

message.

0 No such occurrence.

1 At least one bit sent as dominant is received as recessive.

Loading...

Loading...