RM0046 FlexPWM

Doc ID 16912 Rev 5 661/936

Interrupt Enable register (INTEN)

Table 348. STS field descriptions

Field Description

1

RUF

Registers Updated Flag

This read only flag is set when one of the INIT, VALx, or PRSC fields has been written resulting in non-

coherent data in the set of double buffered registers. Clear RUF by a proper reload sequence

consisting of a reload signal while LDOK = 1. Reset clears RUF.

0 No register update has occurred since last reload.

1 At least one of the double buffered registers has been updated since the last reload.

2

REF

Reload Error Flag

This read/write flag is set when a reload cycle occurs while LDOK is 0 and the double buffered

registers are in a non-coherent state (RUF = 1). Clear REF by writing a logic one to the REF bit. Reset

clears REF.

0 No reload error occurred.

1 Reload signal occurred with non-coherent data and LDOK = 0.

3

RF

Reload Flag

This read/write flag is set at the beginning of every reload cycle regardless of the state of the LDOK

bit. Clear RF by writing a logic one to the RF bit when VALDE is clear (non-DMA mode). RF can also

be cleared by the DMA done signal when VALDE is set (DMA mode). Reset clears RF.

0 No new reload cycle since last RF clearing.

1 New reload cycle since last RF clearing.

10:15

CMPF

Compare Flags

These bits are set when the submodule counter value matches the value of one of the VALx registers.

Clear these bits by writing a 1 to a bit position.

0 No compare event has occurred for a particular VALx value.

1 A compare event has occurred for a particular VALx value.

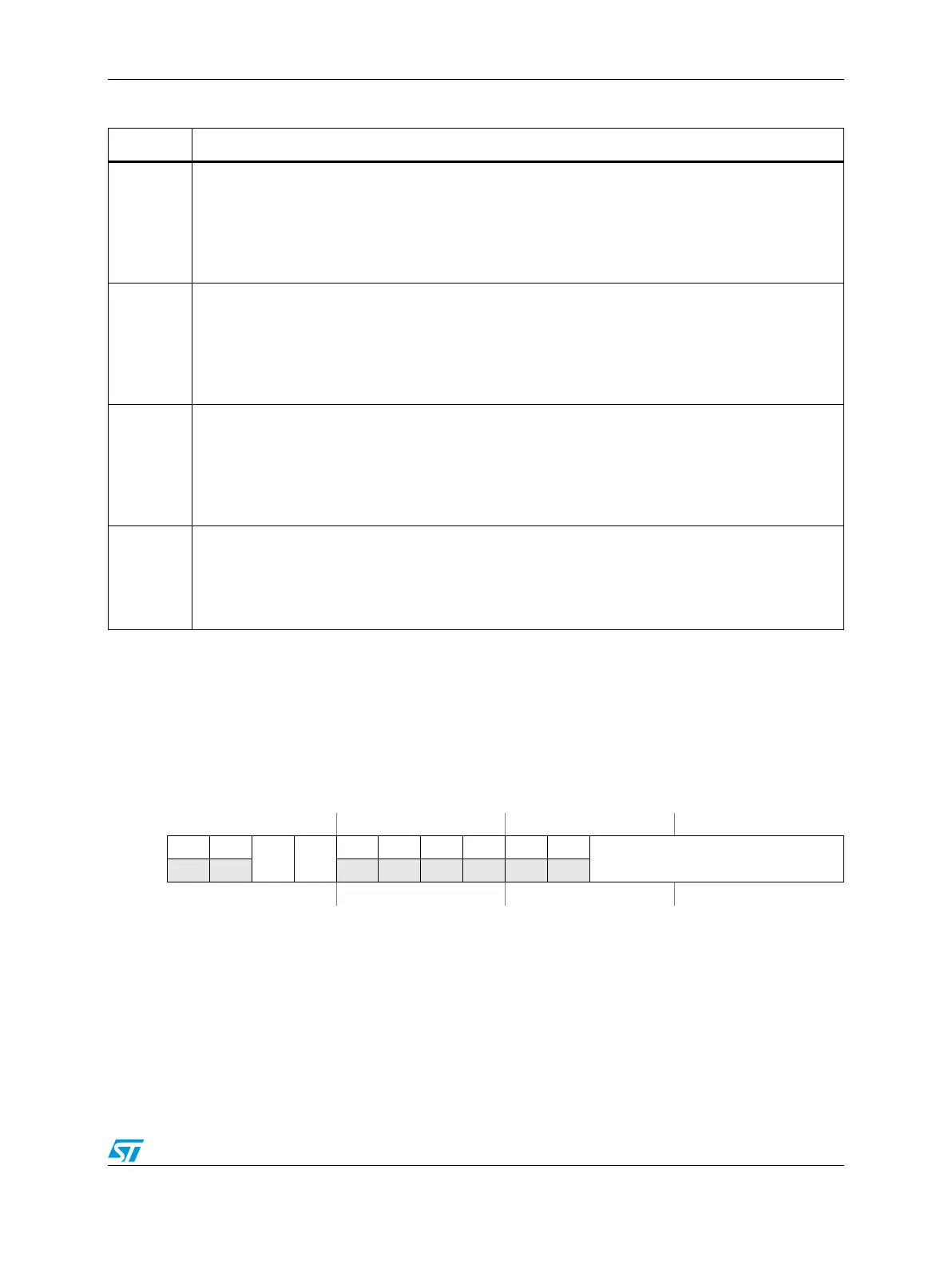

Figure 347. Interrupt Enable register (INTEN)

Address:

Base + 0x001C (Submodule 0)

Base + 0x006C (Submodule 1)

Base + 0x00BC (Submodule 2)

Base + 0x010C (Submodule 3) Access: User read/write

0123456789101112131415

R0 0

REIE RIE

000000

CMPIE

W

Reset0000000000000000

Loading...

Loading...