RM0046 Deserial Serial Peripheral Interface (DSPI)

Doc ID 16912 Rev 5 443/936

20.7.2 Registers description

DSPI Module Configuration Register (DSPIx_MCR)

The DSPIx_MCR contains bits that configure attributes of the DSPI operation. The values of

the HALT and MDIS bits can be changed at any time, but their effect begins on the next

frame boundary. The HALT and MDIS bits in the DSPIx_MCR are the only bit values

software can change while the DSPI is running.

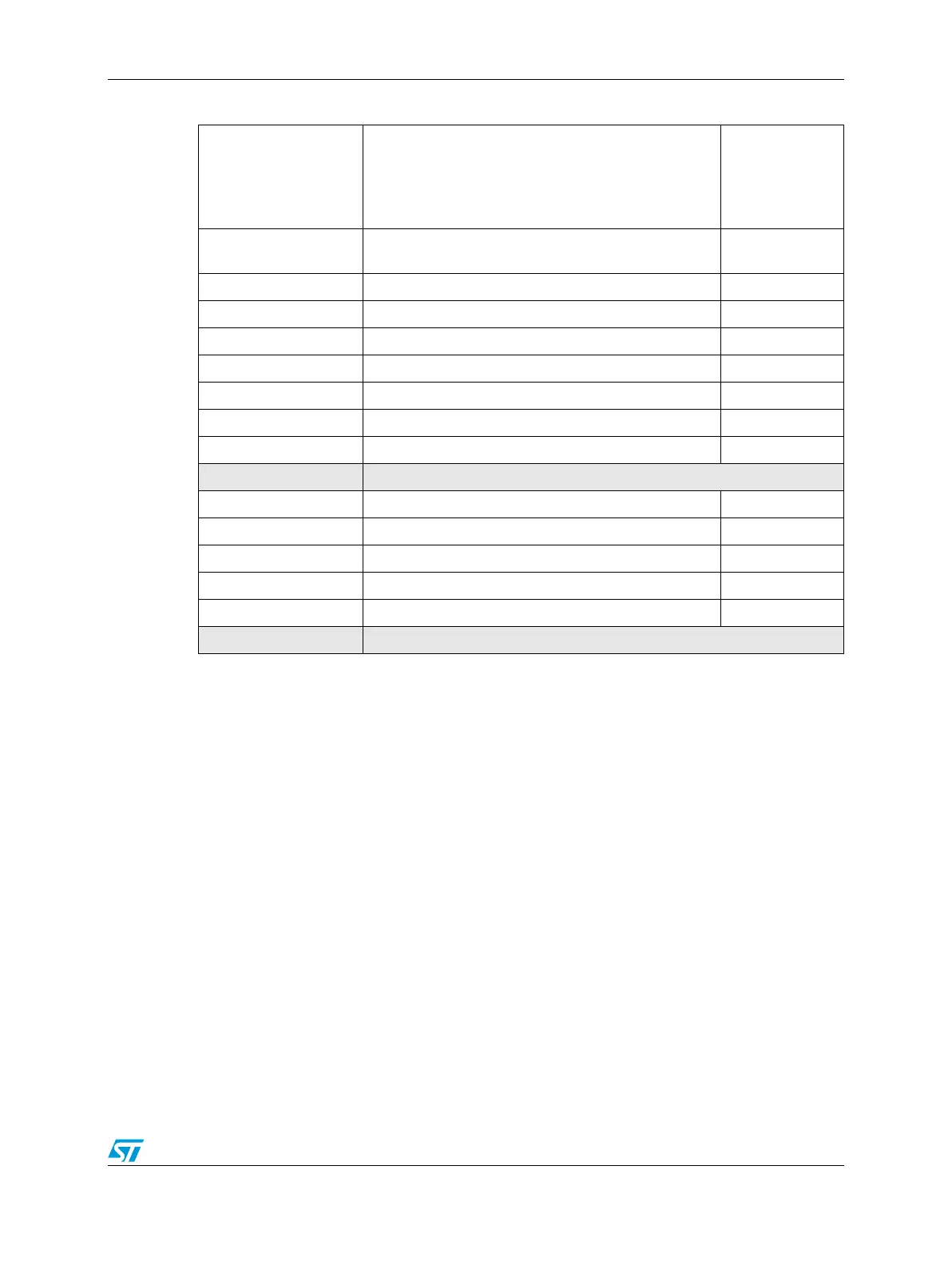

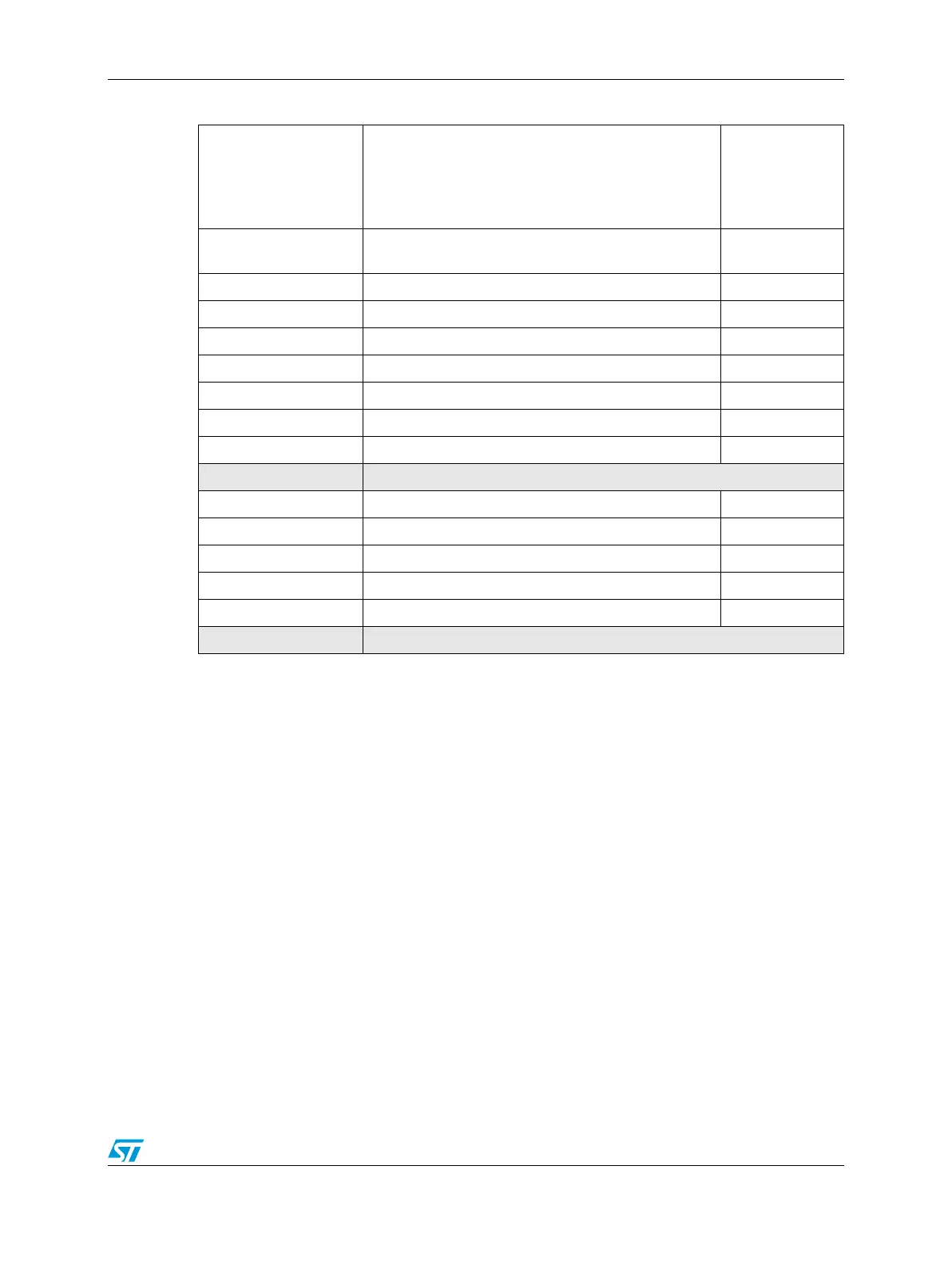

0x0030

DSPI_RSER—DSPI DMA/interrupt request select and

enable register

on page 20-455

0x0034 DSPI_PUSHR—DSPI push TX FIFO register on page 20-456

0x0038 DSPI_POPR—DSPI pop RX FIFO register on page 20-458

0x003C DSPI_TXFR0—DSPI transmit FIFO register 0 on page 20-459

0x0040 DSPI_TXFR1—DSPI transmit FIFO register 1 on page 20-459

0x0044 DSPI_TXFR2—DSPI transmit FIFO register 2 on page 20-459

0x0048 DSPI_TXFR3—DSPI transmit FIFO register 3 on page 20-459

0x004C DSPI_TXFR4—DSPI transmit FIFO register 4 on page 20-459

0x0050–0x007B Reserved

0x007C DSPI_RXFR0—DSPI receive FIFO register 0 on page 20-460

0x0080 DSPI_RXFR1—DSPI receive FIFO register 1 on page 20-460

0x0084 DSPI_RXFR2—DSPI receive FIFO register 2 on page 20-460

0x0088 DSPI_RXFR3—DSPI receive FIFO register 3 on page 20-460

0x008C DSPI_RXFR4—DSPI receive FIFO register 4 on page 20-460

0x0090–0x3FFF Reserved

Table 205. DSPI memory map (continued)

Offset from

DSPI_BASE

0xFFF9_0000 (DSPI_0)

0xFFF9_4000 (DSPI_1)

0xFFF9_8000 (DSPI_2)

Register Location

Loading...

Loading...