RM0046 Deserial Serial Peripheral Interface (DSPI)

Doc ID 16912 Rev 5 459/936

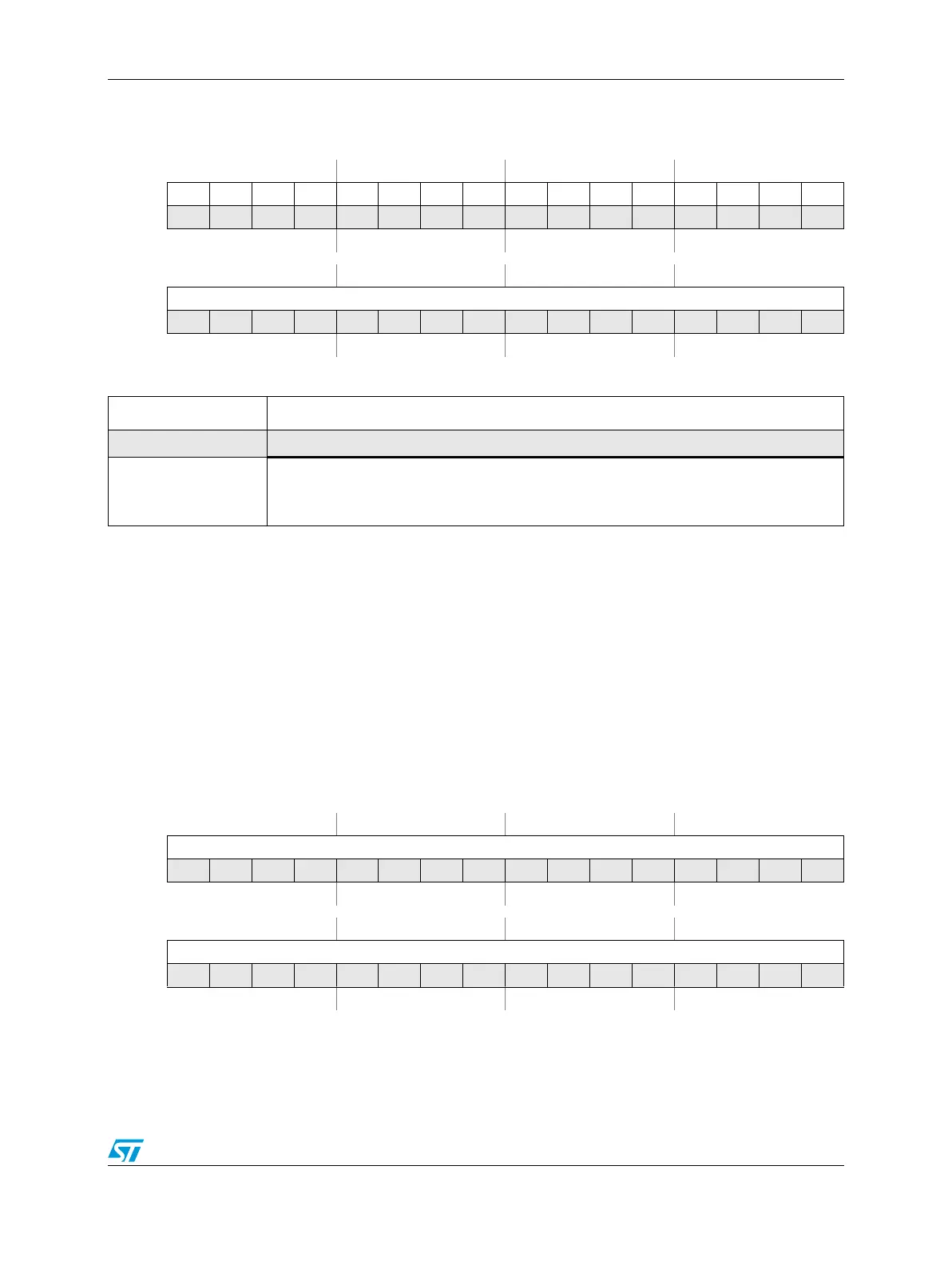

DSPI Transmit FIFO Registers 0–4 (DSPIx_TXFRn)

The DSPIx_TXFRn registers provide visibility into the TX FIFO for debugging purposes.

Each register is an entry in the TX FIFO. The registers are read-only and cannot be

modified. Reading the DSPIx_TXFRn registers does not alter the state of the TX FIFO. The

MCU uses five registers to implement the TX FIFO, that is DSPIx_TXFR0–DSPIx_TXFR4

are used.

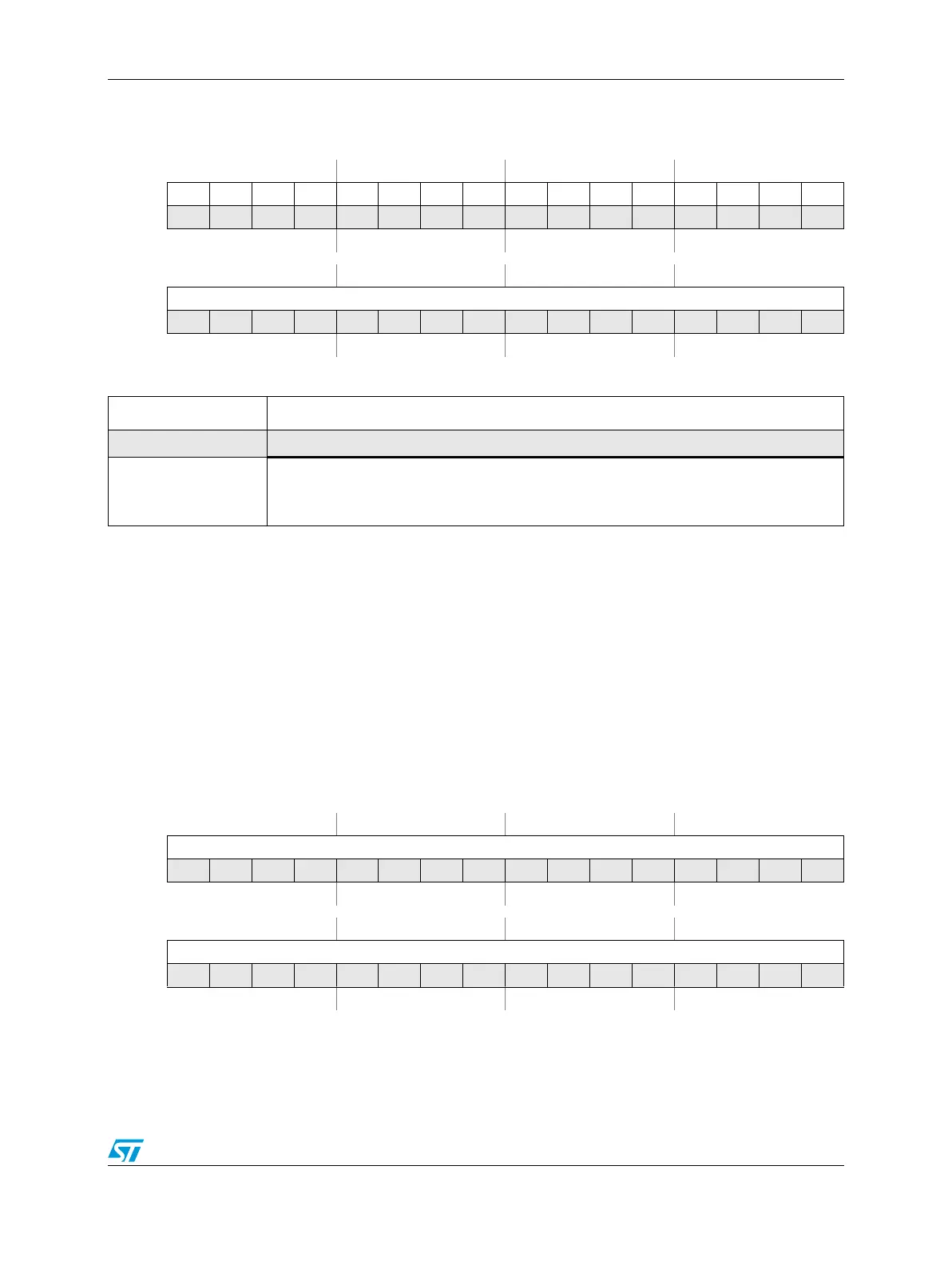

Figure 213. DSPI POP RX FIFO Register (DSPIx_POPR)

Address:

Base + 0x0038 Access: User read-only

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RRXDATA

W

Reset0000000000000000

Table 218. DSPIx_POPR field descriptions

Field Description

0–15 Reserved, must be cleared.

16–31

RXDATA

[0:15]

Received data

The RXDATA field contains the SPI data from the RX FIFO entry pointed to by the pop

next data pointer (POPNXTPTR).

Figure 214. DSPI Transmit FIFO Register 0–4 (DSPIx_TXFRn)

Address:

Base + 0x003C

(DSPIx_TXFR0)

Base + 0x0040 (DSPIx_TXFR1)

Base + 0x0044 (DSPIx_TXFR2)

Base + 0x0048 (DSPIx_TXFR3)

Base + 0x004C

(DSPIx_TXFR4)

Access: User read-only

012 456789101112131415

RTXCMD

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RTXDATA

W

Reset0000000000000000

Loading...

Loading...