RM0046 LIN Controller (LINFlex)

Doc ID 16912 Rev 5 505/936

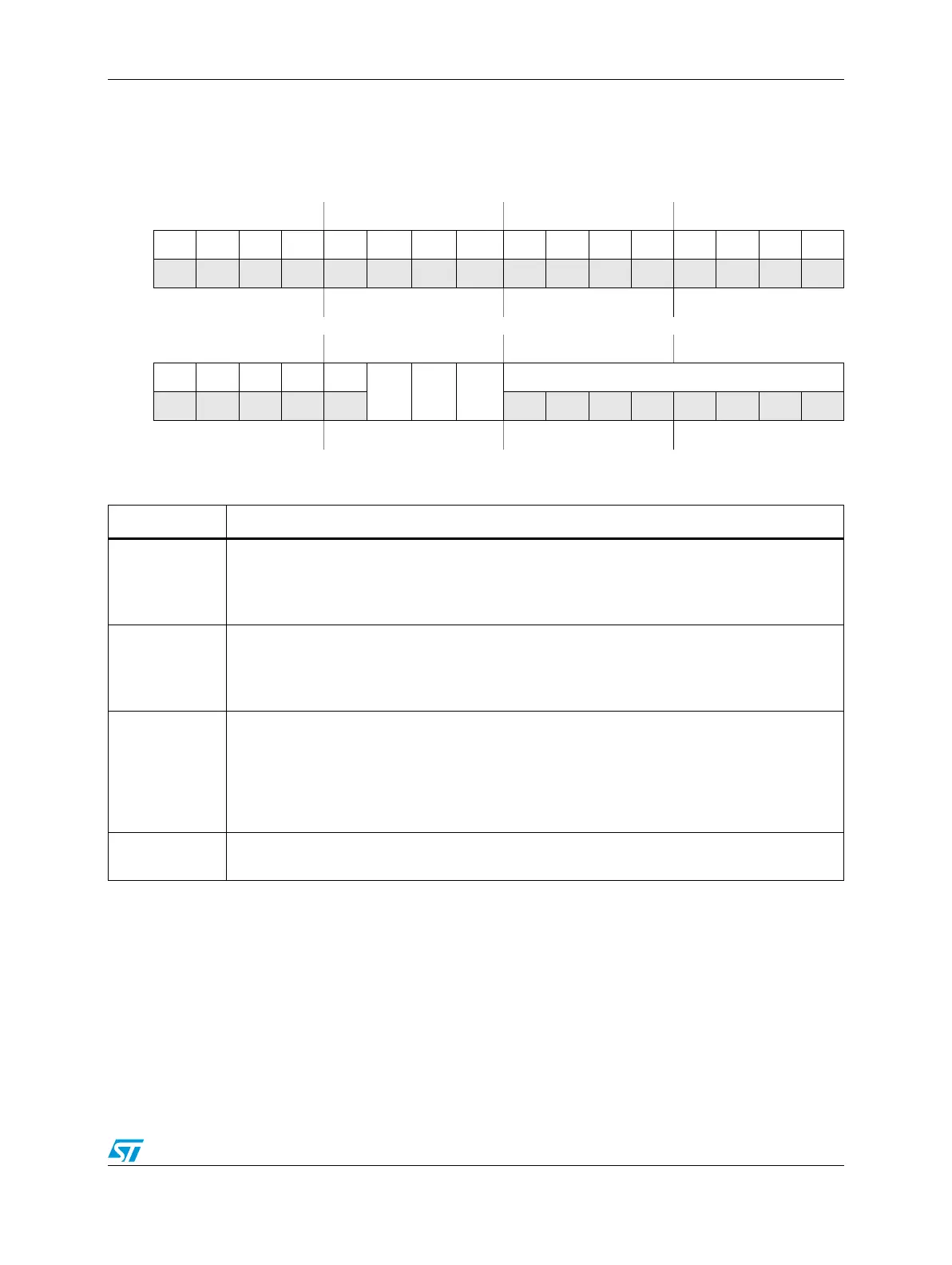

LIN timeout control status register (LINTCSR)

Figure 241. LIN timeout control status register (LINTCSR)

Offset: 0x0018 Access: User read/write

012345 6 7 89101112131415

R 0000000 000000000

W

Reset000000 0 0 00000000

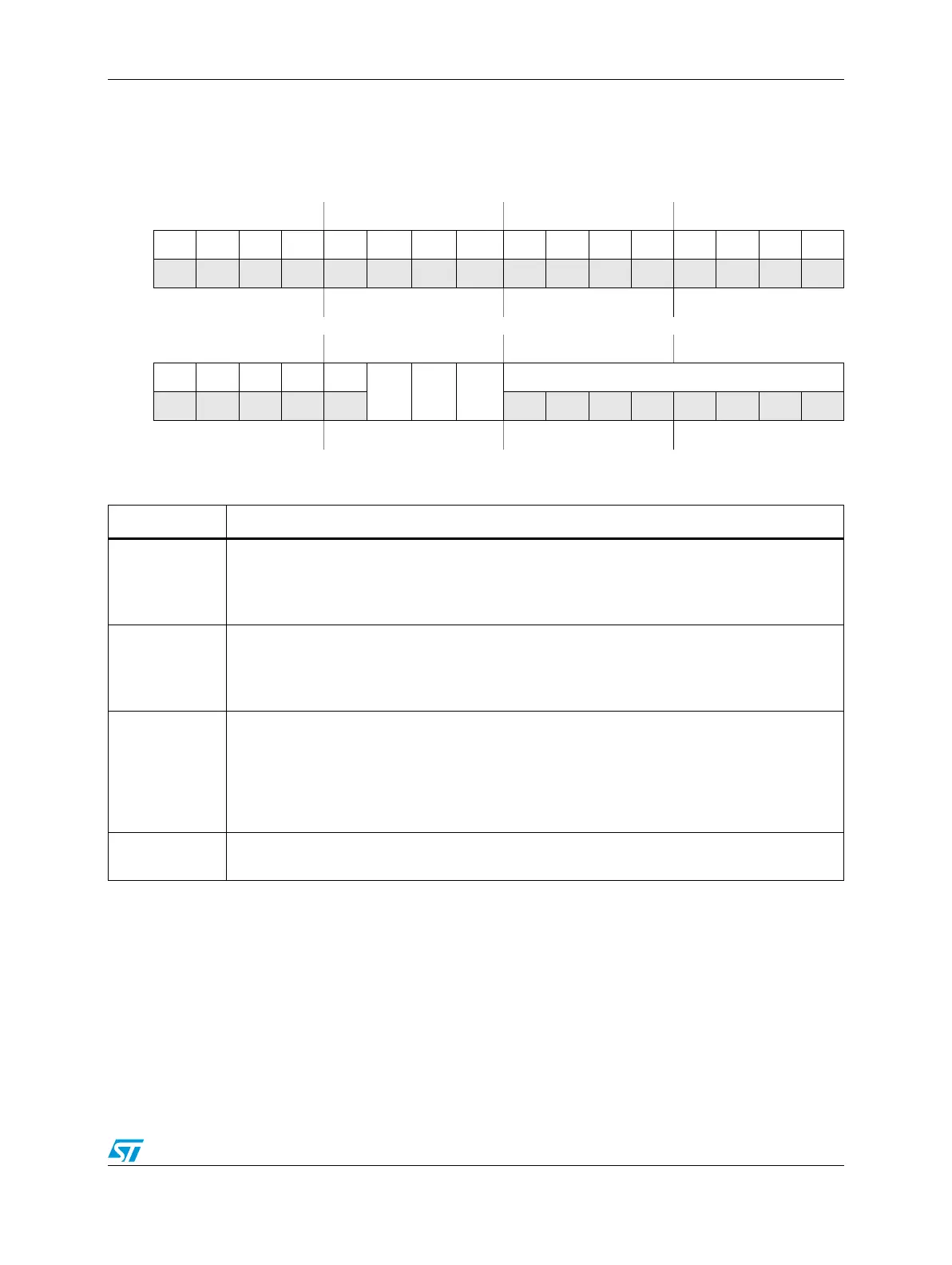

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 00000

LTOM

IOT TOCE

CNT

W

Reset000000 0 0 00100000

Table 243. LINTCSR field descriptions

Field Description

LTO M

LIN timeout mode

0 LIN timeout mode (header, response and frame timeout detection).

1 Output compare mode.

This bit can be set/cleared in Initialization mode only.

IOT

Idle on Timeout

0 LIN state machine not reset to Idle on timeout event.

1 LIN state machine reset to Idle on timeout event.

This bit can be set/cleared in Initialization mode only.

TOCE

Timeout counter enable

0 Timeout counter disable. OCF bit in LINESR or UARTSR is not set on an output compare

event.

1 Timeout counter enable. OCF bit is set if an output compare event occurs.

TOCE bit is configurable by software in Initialization mode. If LIN state is not Init and if timer is in

LIN timeout mode, then hardware takes control of TOCE bit.

CNT

Counter Value

This field indicates the LIN timeout counter value.

Loading...

Loading...