RM0046 Nexus Development Interface (NDI)

Doc ID 16912 Rev 5 883/936

resource(s) via DBERC0), a set bit in DBSR which is software-owned other than MRR or

VLES will cause a debug interrupt to be generated.

Debug status bits in DBSR are set by hardware-owned debug events only while External

Debug Mode is enabled (DBCR0

EDM

=1).

If DBERC0

IDM

=1, all DBSR status bits corresponding to hardware-owned debug events are

masked to ‘0’ when accessed by software. The actual values in the DBSR register is always

visible to hardware when accessed via the OnCE port.

Software-owned resources may be modified by software, but only the corresponding control

and status bits in DBCR0-4 and DBSR are affected by execution of a mtspr, thus only a

portion of these registers may be affected, depending on the allocation settings in DBERC0.

The debug interrupt handler is still responsible for clearing software-owned DBSR bits prior

to returning to normal execution. Hardware always has full access to all registers and

register fields through the OnCE register access mechanism, and it is up to the debug

firmware to properly implement modifications to these registers with read-modify-write

operations to implement any control sharing with software. Settings in DBERC0 should be

considered by the debug firmware in order to preserve software settings of control and

status registers as appropriate when hardware modifications to the debug registers is

performed.

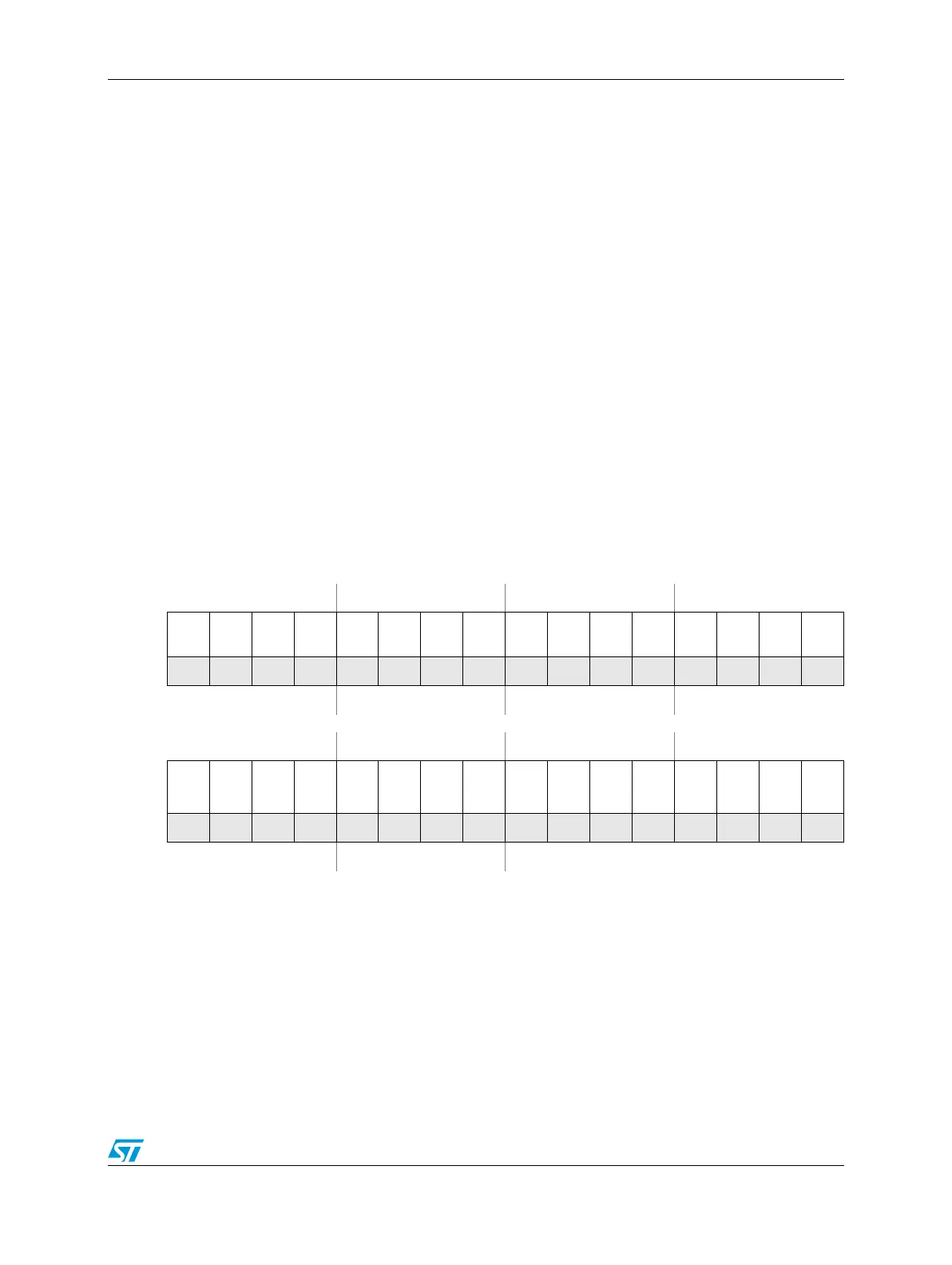

The DBERC0 register is shown in Figure 512.

Figure 512. DBERC0 Register

(1)

SPR - 569

0123456789101112131415

R0

IDM

RST

UDE

ICMP

BRT

IRPT

TRAP

IAC1

IAC2

IAC3

IAC4

DAC1

0

DAC2

0

W

Reset

(2)

0001000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

RET

0000

DEVT1

DEVT2

00

CIRPT

CRET

BKPT

000

FT

W

Reset0000000000000000

1. Read-only by Software; Reset - Unaffected by p_reset_b, cleared by m_por or while in the test-logic-reset OnCE controller

state.

2. Reset by processor reset p_reset_b if DBCR0

EDM

=0, as well as unconditionally by m_por. If DBCR0

EDM

=1, DBERC0

masks off hardware-owned resources from reset by p_reset_b and only software-owned resources indicated by DBERC0

will be reset by p_reset_b. DBSR

MRR

is always updated by p_reset_b however.

Loading...

Loading...