Boot Assist Module (BAM) RM0046

818/936 Doc ID 16912 Rev 5

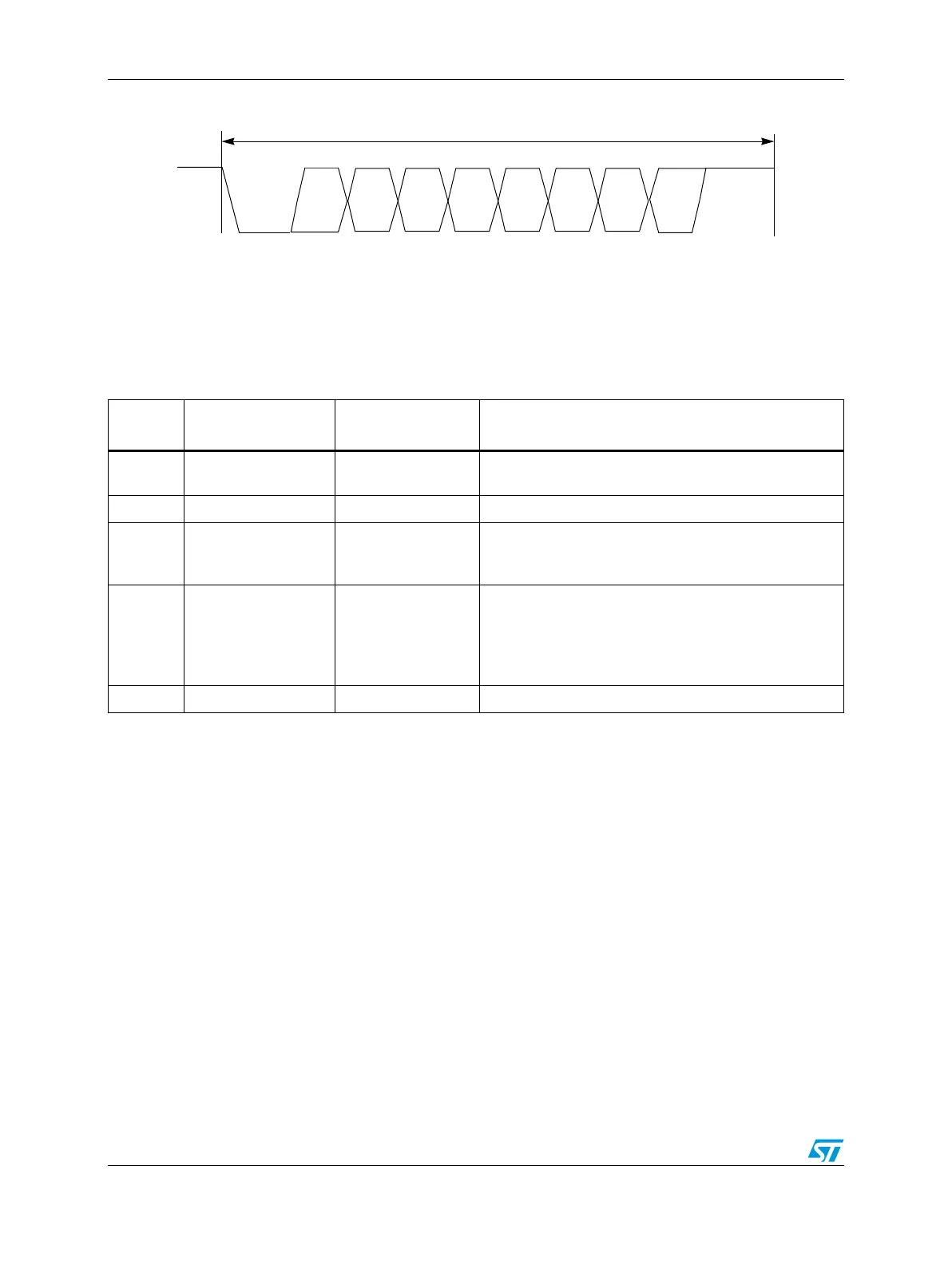

Figure 485. LINFlex bit timing in UART mode

UART boot mode download protocol

Table 441 summarizes the download protocol and BAM action during the UART boot mode.

33.5.7 Bootstrap with FlexCAN—autobaud disabled

Configuration

Boot from FlexCAN protocol is implemented by the FlexCAN_0 module. Pins used are:

● CAN_TX corresponds to pin B[0]

● CAN_RX corresponds to pin B[1].

Boot from FlexCAN with autobaud disabled uses system clock driven by the external

oscillator.

The FlexCAN controller is configured to operate at a baud rate equal to the system clock

frequency/40 (see Ta bl e 4 4 0 for examples of baud rate).

It uses the standard 11-bit identifier format detailed in the FlexCAN 2.0A specification.

FlexCAN controller bit timing is programmed with 10 time quanta, and the sample point is 2

time quanta before the end, as shown in Figure 486.

Start

bit

D0

D7

Stop

bit

Byte Field

D1 D2 D3 D4 D5 D6

Table 441. UART boot mode download protocol (autobaud disabled)

Protocol

step

Host sent

message

BAM response

message

Action

1

64-bit password (MSB

first)

64-bit password

Password checked for validity and compared against

stored password.

2 32-bit store address 32-bit store address Load address is stored for future use.

3

VLE bit +

31-bit number of bytes

(MSB first)

VLE bit +

31-bit number of

bytes (MSB first)

Size of download is stored for future use.

Verify if VLE bit is set to 1.

4

8 bits of raw binary

data

8 bits of raw binary

data

8-bit data are packed into 32-bit word. This word is

saved into SRAM starting from the “Load address”.

“Load address” increments until the number of data

received and stored matches the size as specified in the

previous step.

5 none none Branch to downloaded code.

Loading...

Loading...