RM0046 System Timer Module (STM)

Doc ID 16912 Rev 5 793/936

STM Channel Control Register (STM_CCRn)

The STM Channel Control Register (STM_CCRn) enables and services channel n of the

timer.

STM Channel Interrupt Register (STM_CIRn)

The STM Channel Interrupt Register (STM_CIRn) enables and services channel n of the

timer.

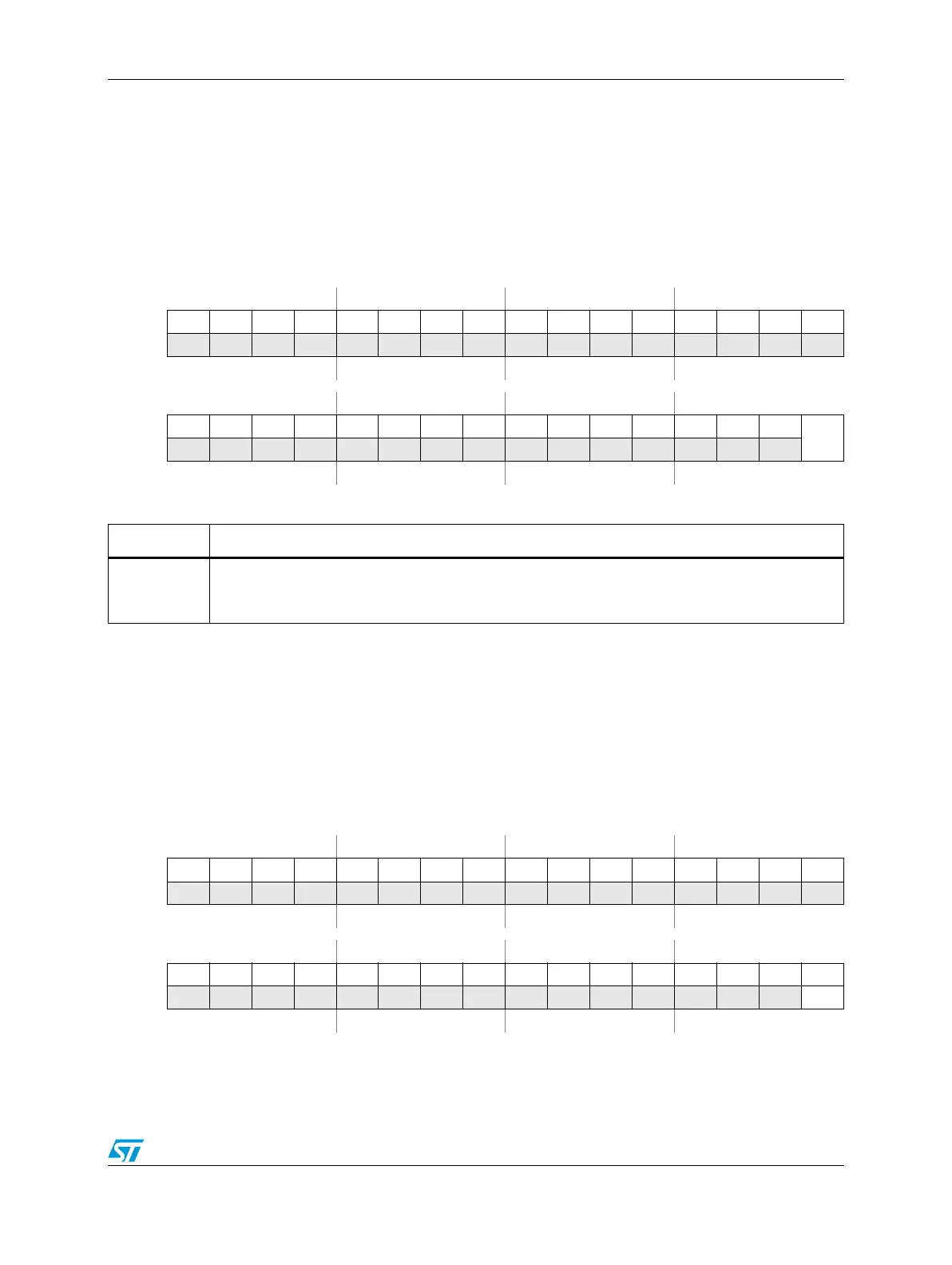

Figure 467. STM Channel Control Register (STM_CCRn)

Address:

Base + 0x0010 (STM_CCR0)

Base + 0x0020 (STM_CCR1)

Base + 0x0030 (STM_CCR2)

Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000 0000000

CEN

W

Reset0000000000000000

Table 426. STM_CCRn field descriptions

Field Description

CEN

Channel Enable

0 The channel is disabled.

1 The channel is enabled.

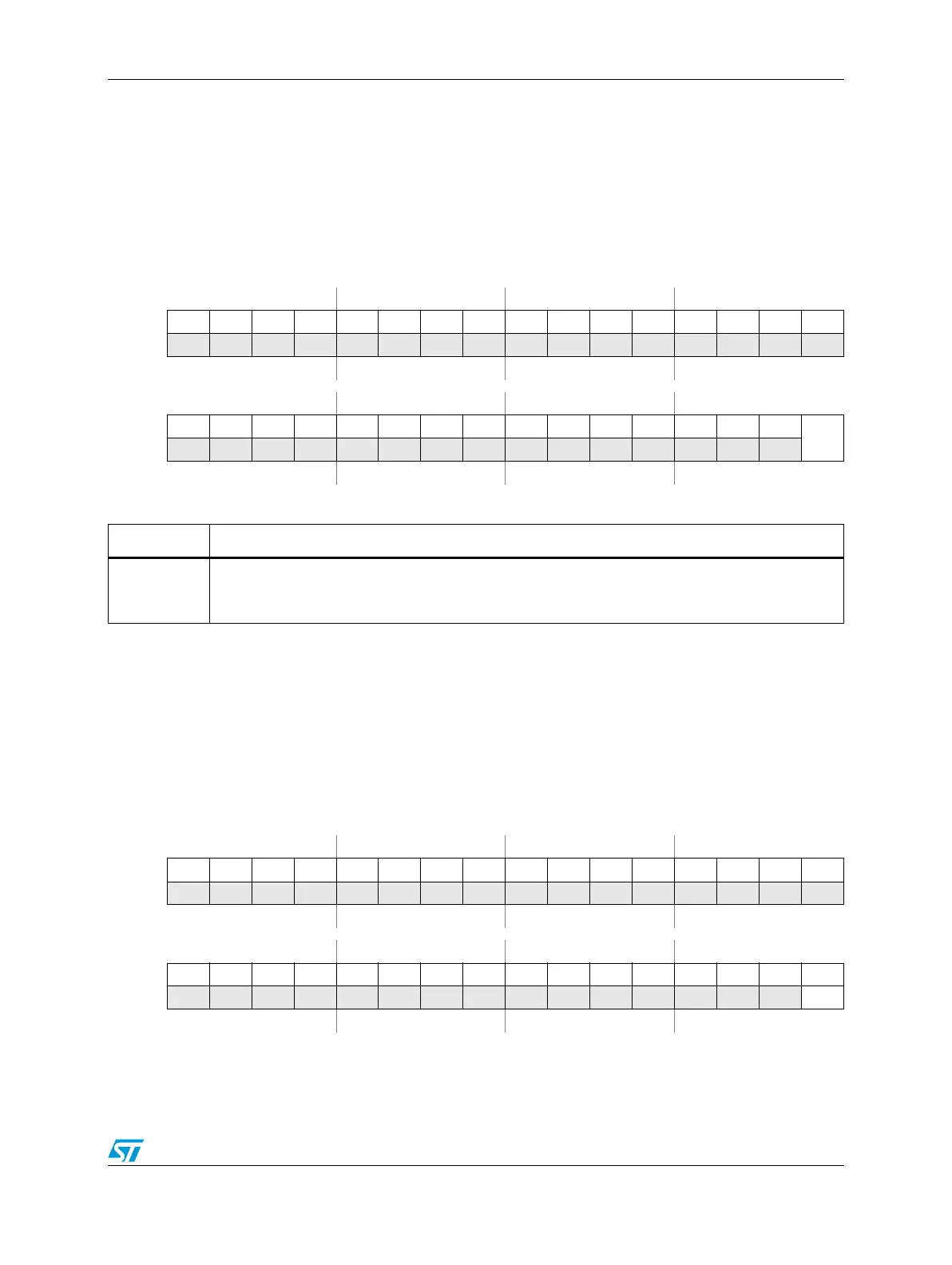

Figure 468. STM Channel Interrupt Register (STM_CIRn)

Address:

Base + 0x0014 (STM_CIR0)

Base + 0x0024 (STM_CIR1)

Base + 0x0034 (STM_CIR2)

Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000 0000000

CIF

W w1c

Reset0000000000000000

Loading...

Loading...