Error Correction Status Module (ECSM) RM0046

302/936 Doc ID 16912 Rev 5

RAM ECC Syndrome Register (RESR)

The RESR is an 8-bit register for capturing the error syndrome of the last properly enabled

ECC event in the RAM memory. Depending on the state of the ECC Configuration Register,

an ECC event in the RAM causes the address, attributes and data associated with the

access to be loaded into the REAR, RESR, REMR, REAT and REDR registers, and the

appropriate flag (R1BC or RNCE) in the ECC Status Register to be asserted.

This register can only be read from the IPS programming model; any attempted write is

ignored.

Note: Table 130 associates the upper 7 bits of the ECC syndrome with the exact data bit in error

for single-bit correctable codewords. This table follows the bit vectoring notation where the

LSB=0. Note that the syndrome value of 0x0001 implies no error condition but this value is

not readable when the PRESR is read for the no error case.

Table 128. REAR field descriptions

Name Description

0-31

REAR[31:0]

RAM ECC Address Register

This 32-bit register contains the faulting access address of the last properly enabled RAM ECC event.

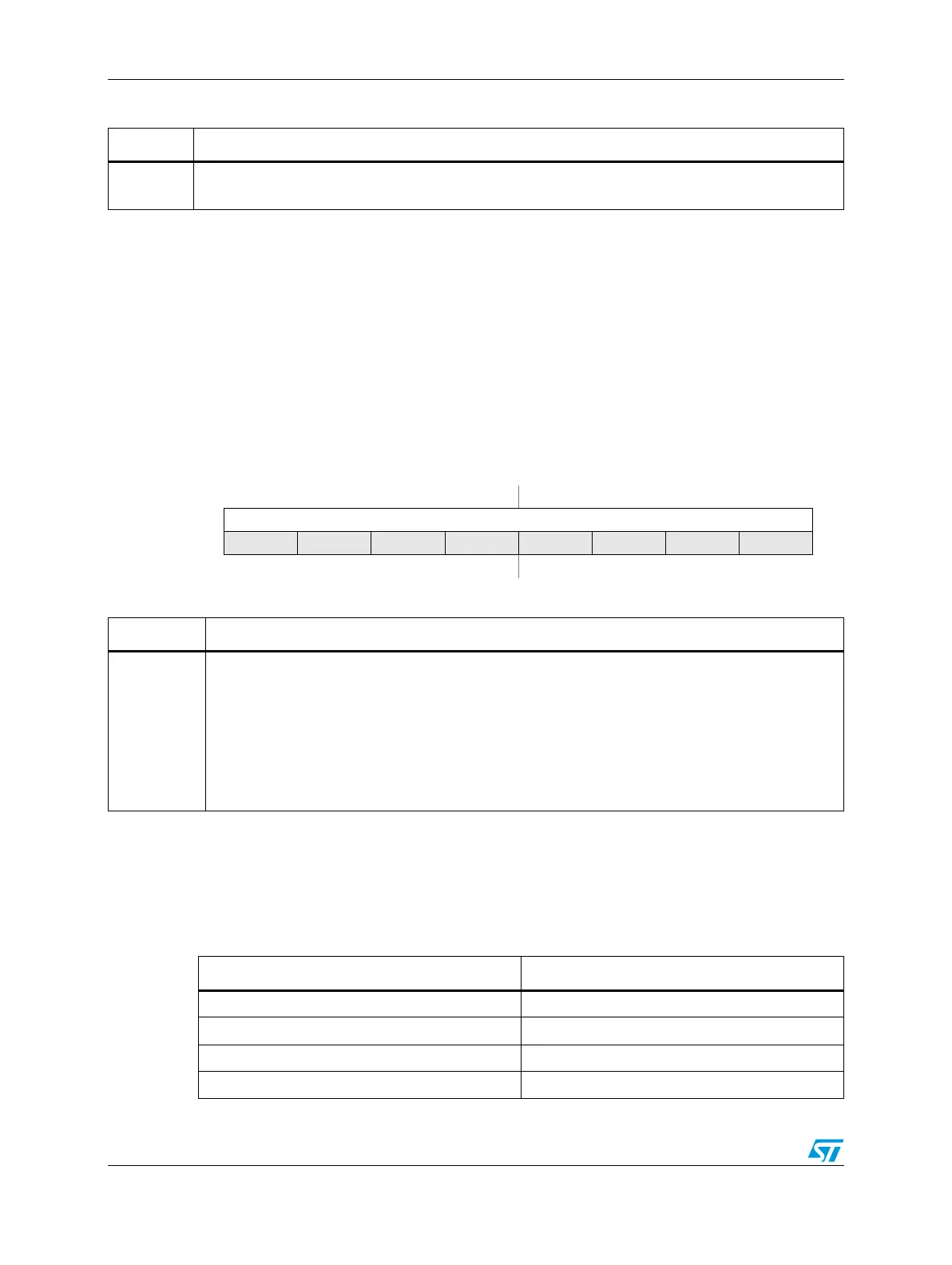

Figure 139. RAM ECC Syndrome Register (RESR)

Address: Base + 0x0065 Access: User read-only

01234567

R RESR[7:0]

W

Reset————————

Table 129. RESR field descriptions

Name Description

0-7

RESR[7:0]

RAM ECC Syndrome Register

This 8-bit syndrome field includes 6 bits of Hamming decoded parity plus an odd-parity bit for the

entire 39-bit (32-bit data + 7 ECC) code word. The upper 7 bits of the syndrome specify the exact bit

position in error for single-bit correctable codewords, and the combination of a non-zero 7-bit

syndrome plus overall incorrect parity bit signal a multi-bit, non-correctable error.

For correctable single-bit errors, the mapping shown in Tabl e 130 associates the upper 7 bits of the

syndrome with the data bit in error.

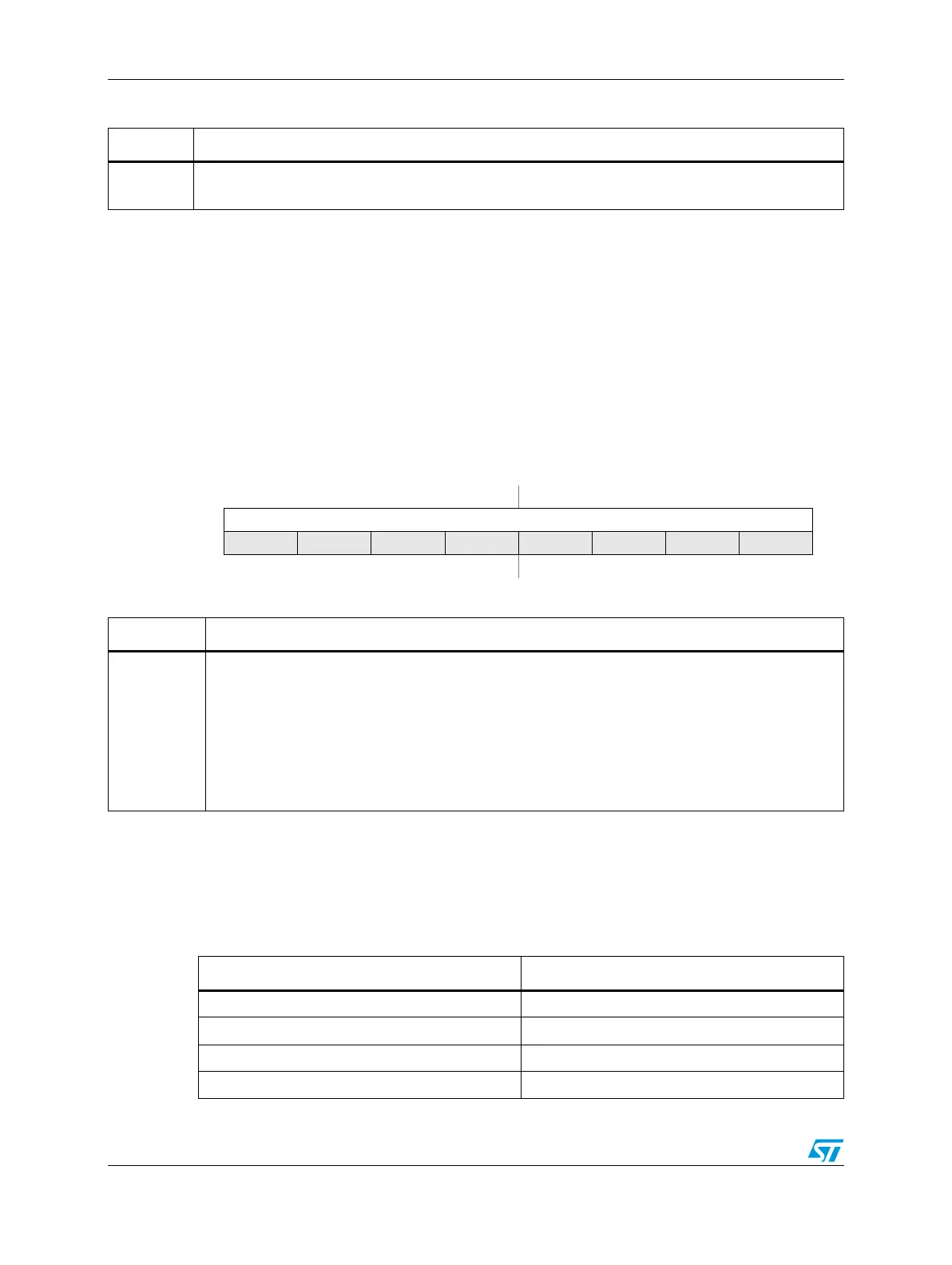

Table 130. RAM syndrome mapping for single-bit correctable errors

RESR[7:0] Data Bit in Error

0x00 ECC ODD[0]

0x01 No Error

0x02 ECC ODD[1]

0x04 ECC ODD[2]

Loading...

Loading...