FlexPWM RM0046

656/936 Doc ID 16912 Rev 5

.

Note: Reading the PRSCx bits reads the buffered values and not necessarily the values currently

in effect. The PRSCx bits take effect at the beginning of the next PWM cycle and only when

the load okay bit, LDOK, is set. This field cannot be written when LDOK is set.

Value register 0 (VAL0)

The 16-bit signed value in this buffered, read/write register defines the mid-cycle reload

point for the PWM in PWM clock periods. This register is not byte accessible.

Note: The VAL0 register is buffered. The value written does not take effect until the LDOK bit is set

and the next PWM load cycle begins. VAL0 cannot be written when LDOK is set. Reading

VAL0 reads the value in a buffer. It is not necessarily the value the PWM generator is

currently using.

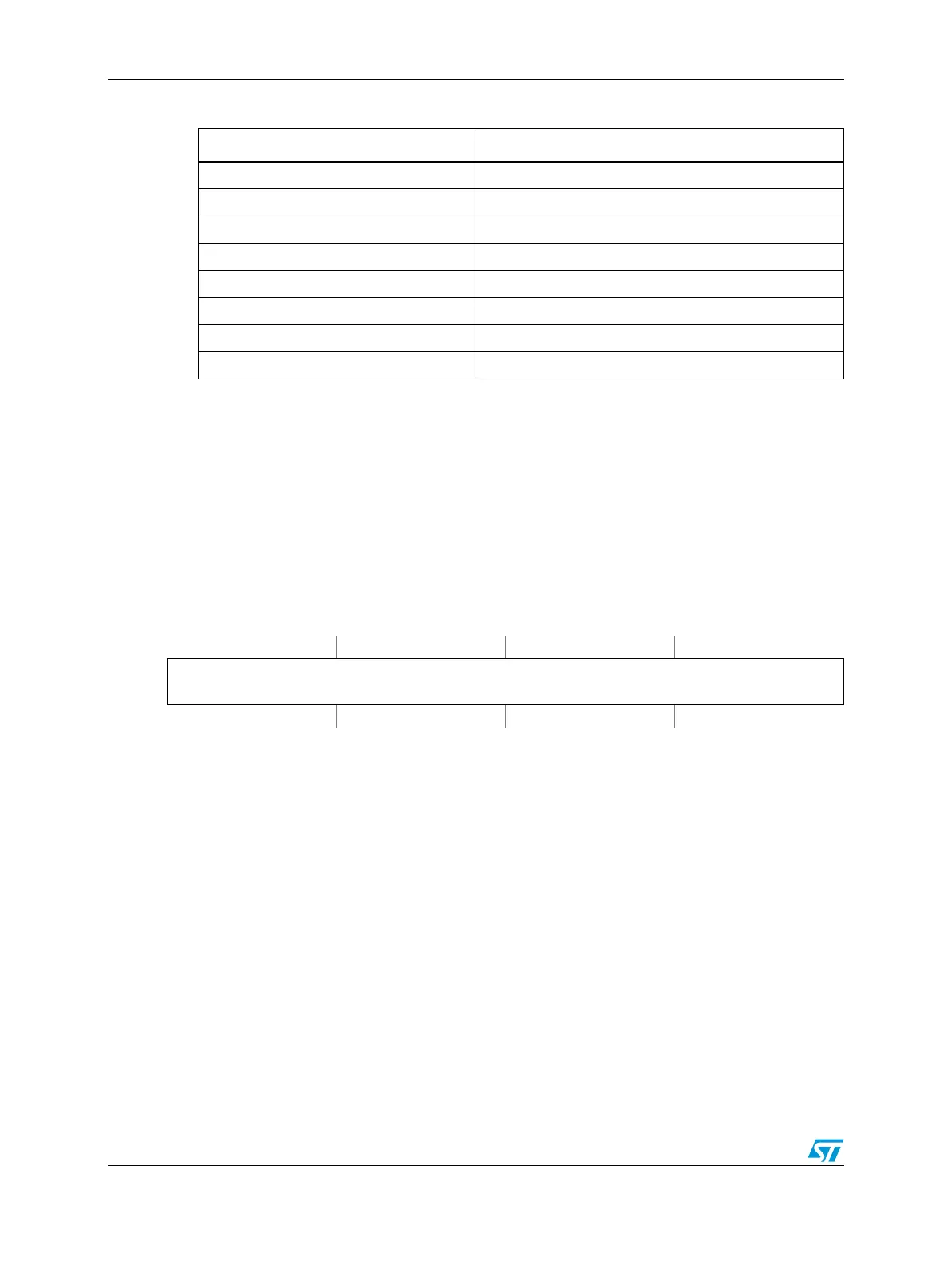

Table 346. PWM prescaler

PRSC PWM clock frequency

000 f

clk

001 f

clk

/2

010 f

clk

/4

011 f

clk

/8

100 f

clk

/16

101 f

clk

/32

110 f

clk

/64

111 f

clk

/128

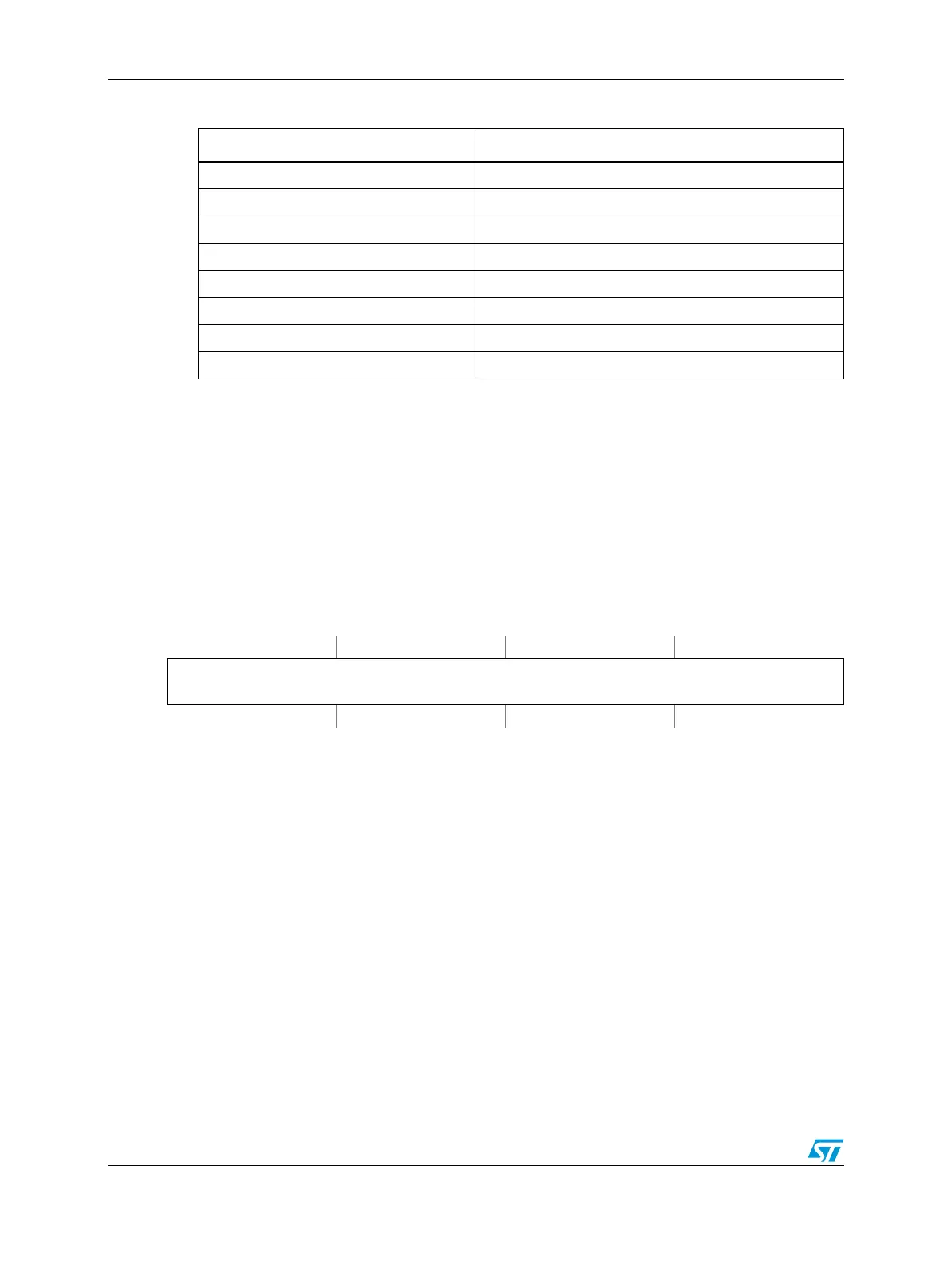

Figure 339. Value Register 0 (VAL0)

Address:

Base + 0x0008 (Submodule 0)

Base + 0x0058 (Submodule 1)

Base + 0x00A8 (Submodule 2)

Base + 0x00F8 (Submodule 3) Access: User read/write

0123456789101112131415

R

VAL0

W

Reset0000000000000000

Loading...

Loading...