RM0046 Flash Memory

Doc ID 16912 Rev 5 359/936

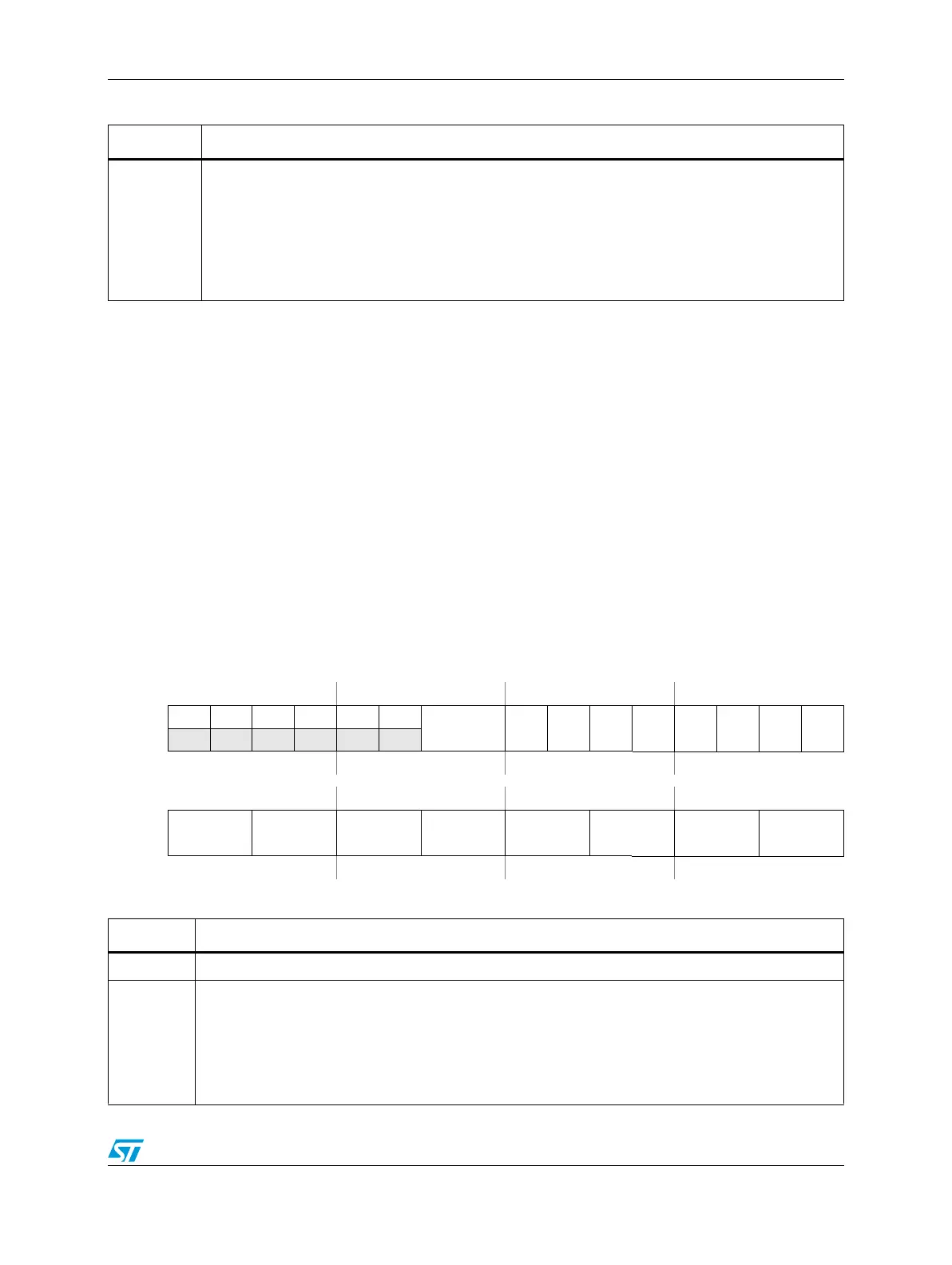

Platform Flash Access Protection Register (PFAPR)

The Platform Flash Access Protection Register (PFAPR) controls read and write accesses

to the Flash based on system master number. Prefetching capabilities are defined on a per

master basis. This register also defines the arbitration mode for controllers supporting two

AHB ports. The register is described in Figure 162 and Table 158.

The contents of the register are loaded from location 0x20_3E00 of the shadow region in the

code Flash (bank0) array at reset. To temporarily change the values of any of the fields in

the PFAPR, a write to the IPS-mapped register is performed. To change the values loaded

into the PFAPR at reset, the word location at address 0x20_3E00 of the shadow region in

the Flash array must be programmed using the normal sequence of operations. The reset

value shown in Table 1 6 2 reflects an erased or unprogrammed value from the shadow

region.

Note: This register is not implemented on the data Flash block.

31

B1_P0_PFE

Bank1, Port 0 Buffer Enable

This bit enables or disables read hits from the 128-bit holding register. It is also used to invalidate the

contents of the holding register. This bit is set by hardware reset, enabling the use of the holding

register.

0 The holding register is disabled from satisfying read requests.

1 The holding register is enabled to satisfy read requests on hits.

Table 157. PFCR1 field descriptions (continued)

Field Description

Figure 162. Platform Flash Access Protection Register (PFAPR)

Address:

Base + 0x0024 Access: User read/write

0123456789101112131415

R000000

ARBM

M7

PFD

M6

PFD

M5

PFD

M4

PFD

M3

PFD

M2

PFD

M1

PFD

M0

PFD

W

Reset0000001111111111

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

M7AP M6AP M5AP M4AP M3AP M2AP M1AP M0AP

W

Reset1111111111111111

Table 158. PFAPR field descriptions

Field Description

0-5 Reserved, should be cleared.

6-7

ARBM

Arbitration Mode

This 2-bit field controls the arbitration for PFlash controllers supporting 2 AHB ports.

00 Fixed priority arbitration with AHB p0 > p1.

01 Fixed priority arbitration with AHB p1 > p0.

1x Round-robin arbitration.

Loading...

Loading...