RM0046 Nexus Development Interface (NDI)

Doc ID 16912 Rev 5 861/936

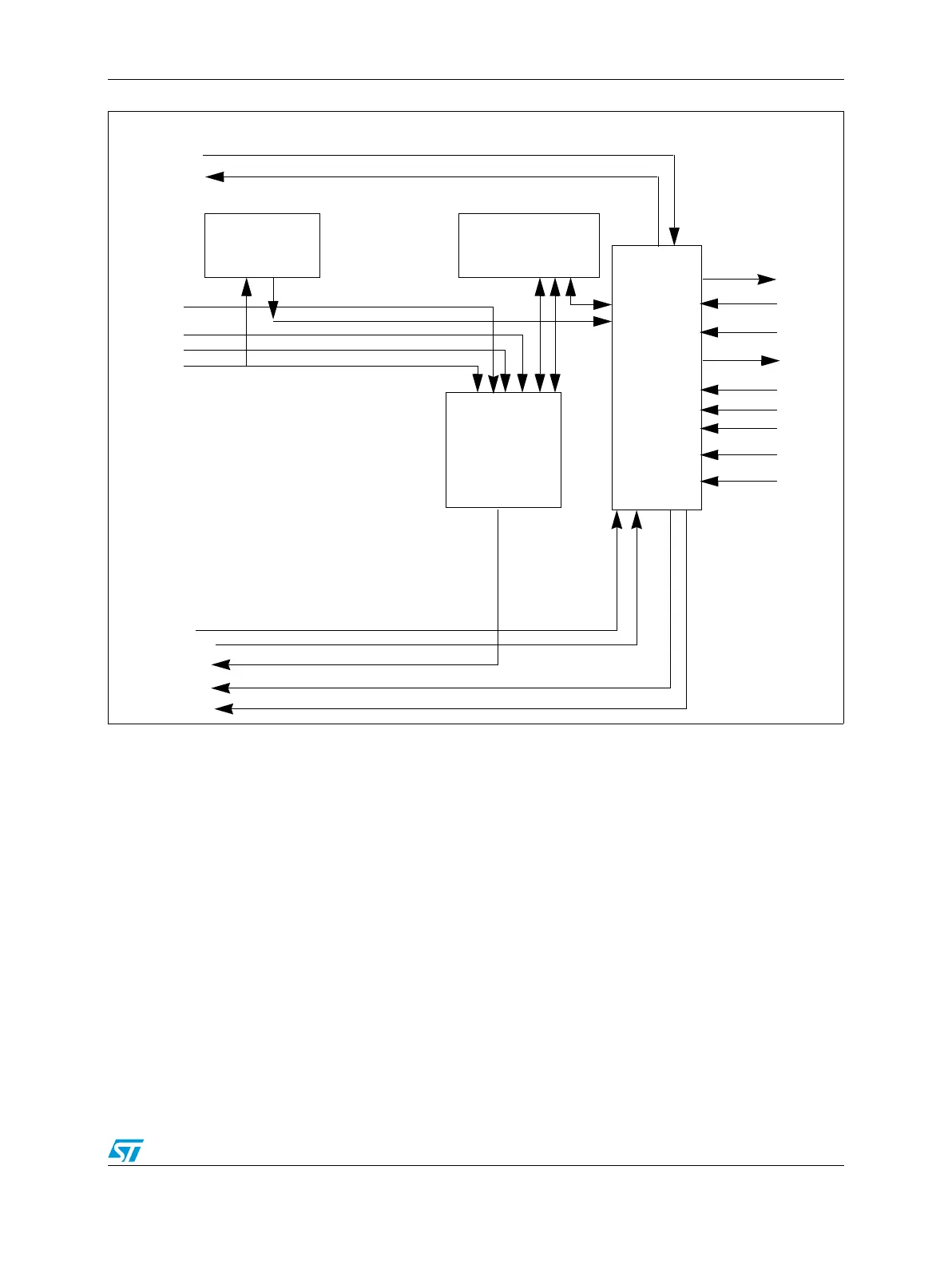

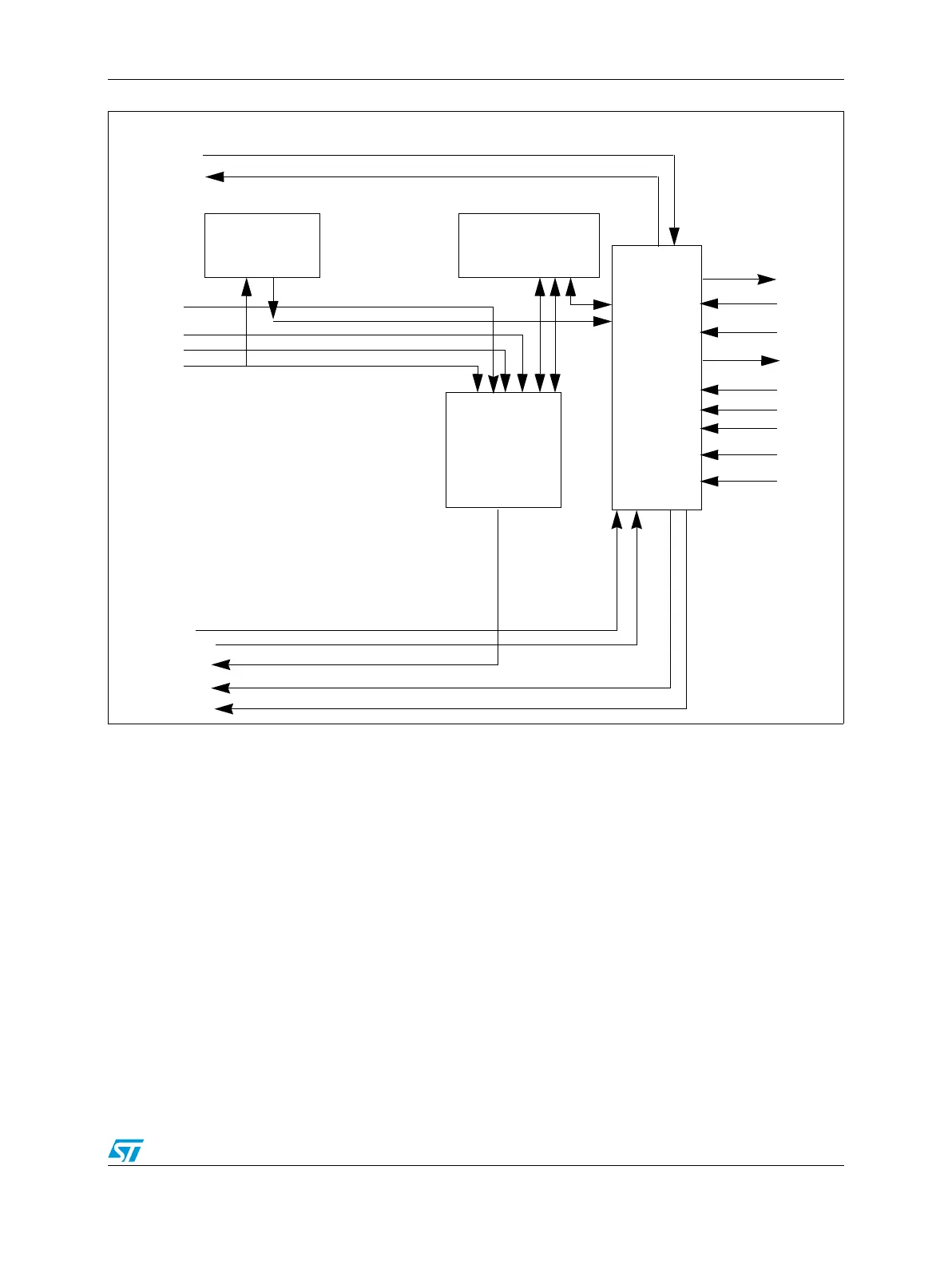

Figure 505. e200z0h Debug Resources

36.10 Software Debug Events and Exceptions

Software debug events and exceptions are available when internal debug mode is enabled

(DBCR0

IDM

=1) and not overridden by external debug mode (DBCR0

EDM

must either be

cleared or corresponding resources must be allocated to software debug by the settings in

DBERC0). When enabled, debug events cause debug exceptions to be recorded in the

Debug Status Register. Specific event types are enabled by the Debug Control Registers

(DBCR0-2). The Unconditional Debug Event (UDE) is an exception to this rule; it is always

enabled. Once a Debug Status Register (DBSR) bit is set corresponding to a debug

resource which is “owned” by software (other than MRR), if Debug interrupts are enabled by

MSR

DE

, a Debug interrupt will be generated. The debug interrupt handler is responsible for

ensuring that multiple repeated debug interrupts do not occur by clearing the DBSR as

appropriate.

Certain debug events are not allowed to occur when MSR

DE

=0 and DBCR0

EDM

=0. In such

situations, no debug exception occurs and thus no DBSR bit is set. Other debug events may

PSTAT#

ATTR#

ADDR#

.

.

.

j_tdo, j_tdo_en

j_tdi

j_tclk

Breakpoint and

Trace Logic

OnCE

Controller

and

Serial

Interface

Debug

Registers

and

Comparators

Pipeline

Information

j_tms

dbg_dbgrq

cpu_dbgack

jd_watchpt[0:n]

#-internal signals

to/from CPU only

p_devt[1,2]

j_trst_b

jd_de_en

jd_debug_b

DATA#

jd_en_once

jd_de_b

jd_mclk_on

p_ude

Loading...

Loading...