Error Correction Status Module (ECSM) RM0046

296/936 Doc ID 16912 Rev 5

In the event that multiple status flags are signaled simultaneously, ECSM records the event

with the R1BC as highest priority, then F1BC, then RNCE, and finally FNCE.

ECC Error Generation Register (EEGR)

The ECC error generation register is a 16-bit control register used to force the generation of

single- and double-bit data inversions in the memories with ECC, most notably the RAM.

This capability is provided for two purposes:

● It provides a software-controlled mechanism for injecting errors into the memories

during data writes to verify the integrity of the ECC logic.

● It provides a mechanism to allow testing of the software service routines associated

with memory error logging.

It should be noted that while the EEGR is associated with the RAM, similar capabilities exist

for the flash, that is, the ability to program the non-volatile memory with single- or double-bit

errors is supported for the same two reasons previously identified.

For both types of memories (RAM and flash), the intent is to generate errors during data

write cycles, such that subsequent reads of the corrupted address locations generate ECC

events, either single-bit corrections or double-bit non-correctable errors that are terminated

with an error response.

The enabling of these error generation modes requires the same input enable signal (as that

used to enable single-bit correction reporting) be asserted. This signal is tied to 1 at SoC

level and hence reporting of single-bit memory corrections is always enabled.

6

RNCE

RAM Non-Correctable Error

The occurrence of a properly enabled non-correctable RAM error generates a ECSM ECC interrupt

request. The faulting address, attributes and data are also captured in the REAR, RESR, REMR,

REAT and REDR registers. To clear this interrupt flag, write a 1 to this bit. Writing a 0 has no effect.

This bit can only be set if ECR[ERNCR] is asserted.

0 No reportable non-correctable RAM error detected

1 Reportable non-correctable RAM error detected

7

FNCE

Flash Non-Correctable Error

The occurrence of a properly enabled non-correctable flash error generates a ECSM ECC interrupt

request. The faulting address, attributes and data are also captured in the FEAR, FEMR, FEAT and

FEDR registers. To clear this interrupt flag, write a 1 to this bit. Writing a 0 has no effect. This bit can

only be set if ECR[ERNCR] is asserted.

0 No reportable non-correctable flash error detected

1 Reportable non-correctable flash error detected

Table 122. ESR field descriptions (continued)

Field Description

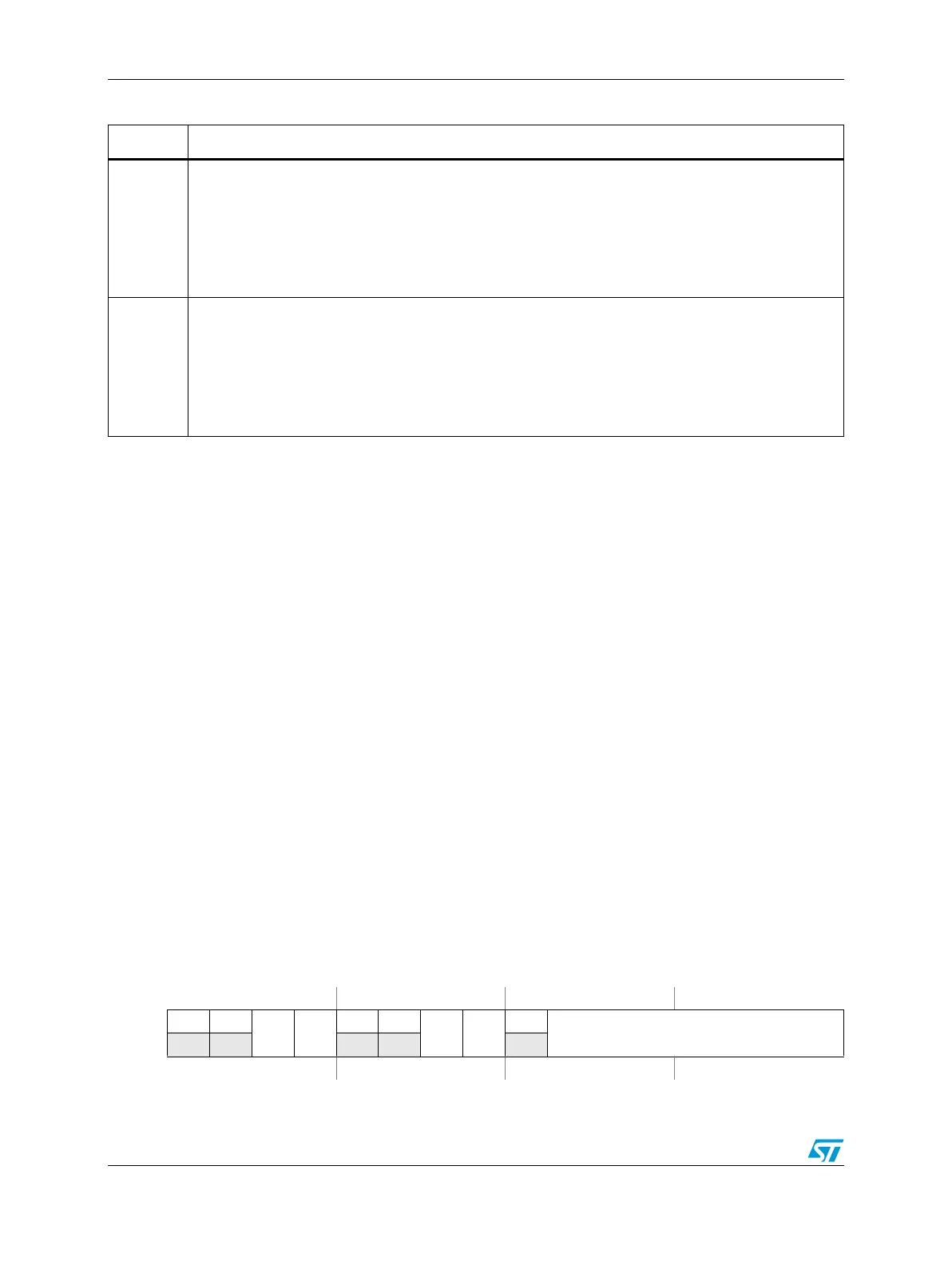

Figure 133. ECC Error Generation register (EEGR)

Address Base + 0x004A Access: User read/write

0123456789101112131415

R0 0

FRC

1BI

FR11

BI

00

FRC

NCI

FR1

NCI

0

ERRBIT[6:0]

W

Reset0000000000000000

Loading...

Loading...