Clock Description RM0046

98/936 Doc ID 16912 Rev 5

Upon the detection of one of the above mentioned failures, the SPC560P40/34 device either

asserts a reset, generates an interrupt, or sends the device into the SAFE state.

The reaction to each of the clock failures and system parameters (like active clocks and

SYS_CLK clock source) that become active in SAFE state are under software control and

can be configured in the ME module.

4.6 IRC 16 MHz internal RC oscillator (RC_CTL)

The IRC output frequency can be trimmed using RCTRIM bits. After a power-on reset, the

IRC is trimmed using a factory test value stored in test flash memory. However, after a

power-on reset the test flash memory value is not visible at RC_CTL[RCTRIM], and this field

shows a value of zero. Therefore, be aware that the RC_CTL[RCTRIM] field does not reflect

the current trim value until you have written to it. Pay particular attention to this feature when

you initiate a read-modify-write operation on RC_CTL, because a RCTRIM value of zero

may be unintentionally written back and this may alter the IRC frequency. In this case, you

should calibrate the IRC using the CMU.

In this oscillator, two's complement trimming method is implemented. So the trimming code

increases from -32 to 31. As the trimming code increases, the internal time constant

increases and frequency reduces. Please refer to device datasheet for average frequency

variation of the trimming step.

4.7 XOSC external crystal oscillator

The external crystal oscillator (XOSC) operates in the range of 4 MHz to 40 MHz. The

XOSC digital interface contains the control and status registers accessible for the external

crystal oscillator.

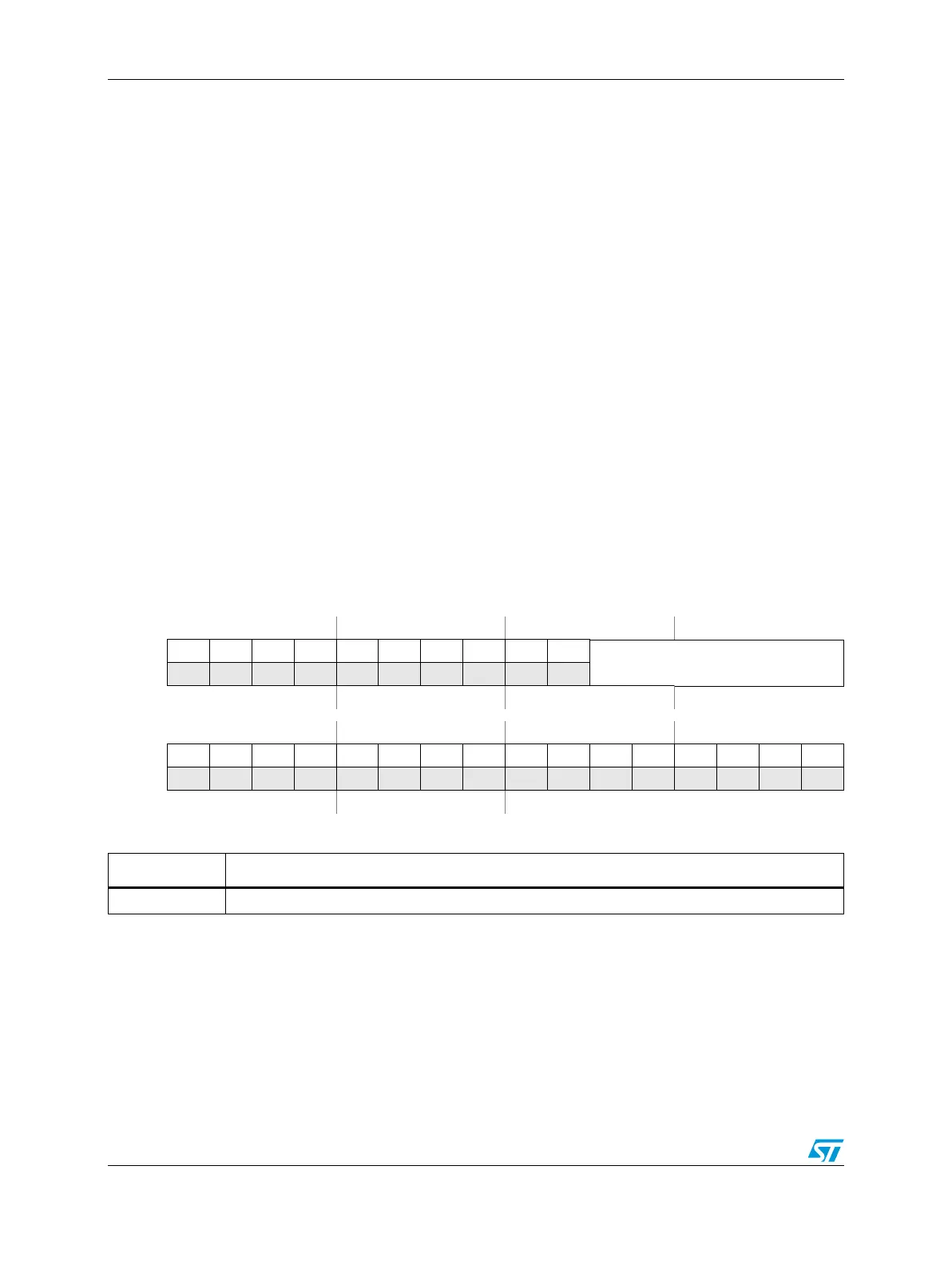

Figure 12. RC Control register (RC_CTL)

Address:

0xC3FE_0060

(Base + 0x0000)

Access: Supervisor read/write; User read-

only

0123456789101112131415

R00000000 00

RCTRIM[5:0]

W

Reset0000000000000000

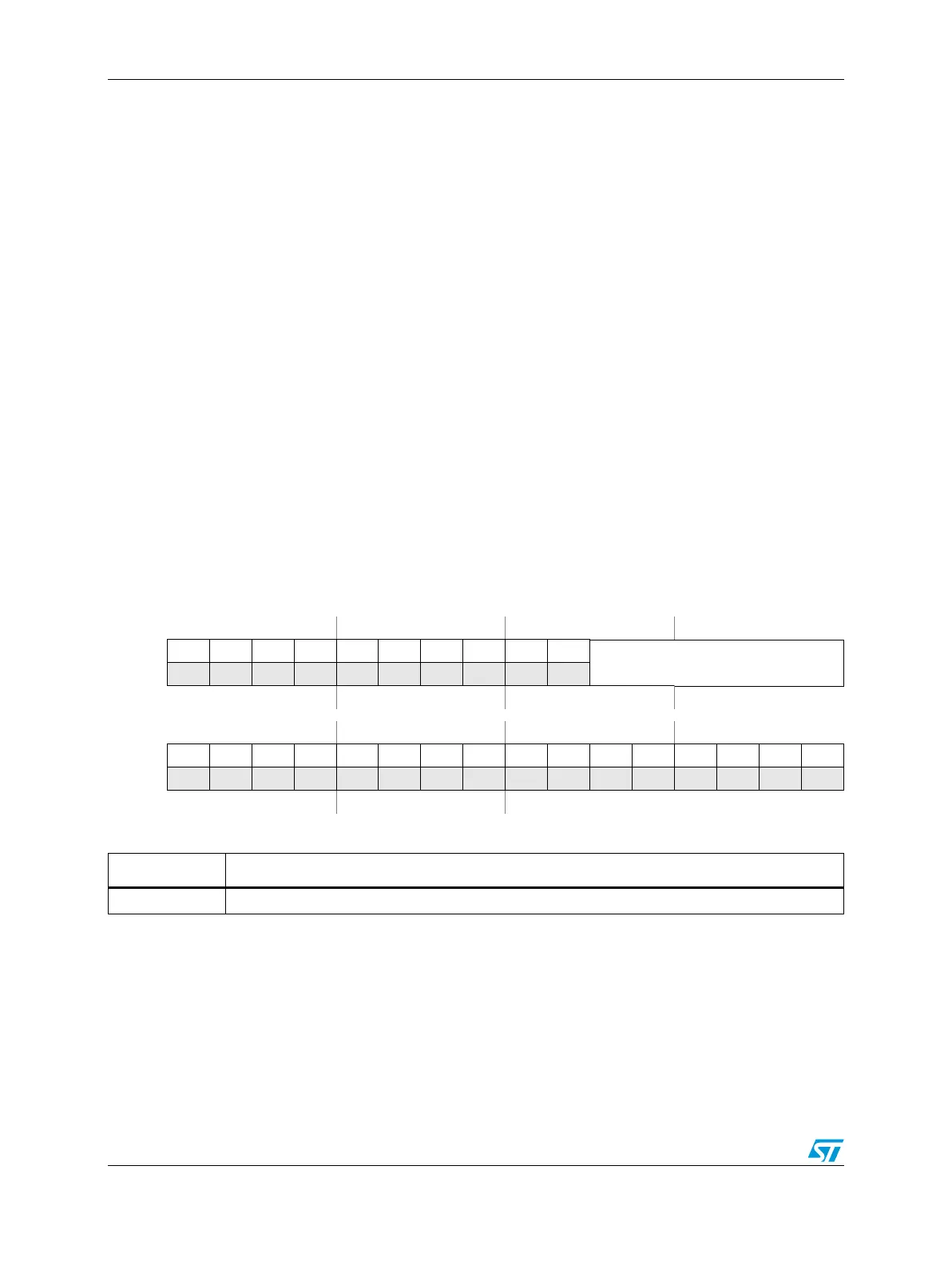

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000 00000000

W

Reset0000000000000000

Table 8. RC_CTL field descriptions

Field Description

RCTRIM[5:0] Main RC trimming bits

Loading...

Loading...