Nexus Development Interface (NDI) RM0046

894/936 Doc ID 16912 Rev 5

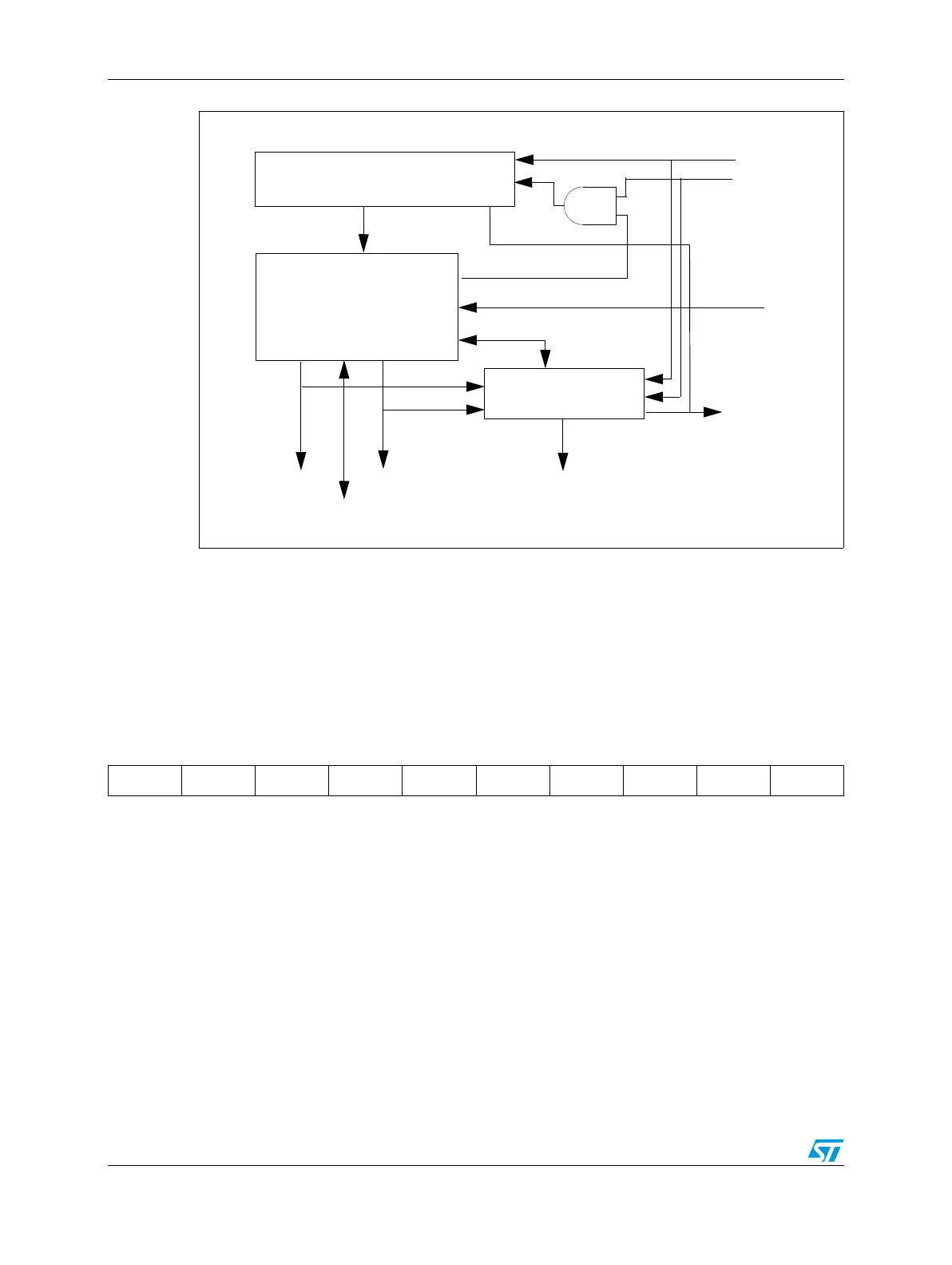

Figure 515. e200z0h OnCE Controller and Serial Interface

e200z0h OnCE Status Register

Status information regarding the state of the e200z0h CPU is latched into the OnCE Status

register when the OnCE controller state machine enters the Capture-IR state. When OnCE

operation is enabled, this information is provided on the j_tdo output in serial fashion when

the Shift_IR state is entered following a Capture-IR. Information is shifted out least

significant bit first.

OnCE COMMAND REGISTER

TDI

TCLK

STATUS AND CONTROL

REGISTERS

TDO

MODE SELECT

OnCE DECODER

REG WRITE

REG READ

.

.

.

.

CPU CONTROL/STATUS

UPDATE

.

MCLK ERR CHKSTOP RESET HALT STOP DEBUG WAIT 0 1

0123456789

Figure 516. OnCE Status Register

Loading...

Loading...