Error Correction Status Module (ECSM) RM0046

294/936 Doc ID 16912 Rev 5

ECC Status Register (ESR)

The ECC Status Register is an 8-bit control register for signaling which types of properly

enabled ECC events have been detected. The ESR signals the last properly enabled

memory event to be detected. ECC interrupt generation is separated into single-bit error

detection/correction, uncorrectable error detection, and the combination of the two as

defined by the following boolean equations:

ECSM_ECC1BIT_IRQ

= ECR[ER1BR] & ESR[R1BC]// ram, 1-bit correction

| ECR[EF1BR] & ESR[F1BC]// flash, 1-bit correction

ECSM_ECCRNCR_IRQ

= ECR[ERNCR] & ESR[RNCE]// ram, noncorrectable error

ECSM_ECCFNCR_IRQ

= ECR[EFNCR] & ESR[FNCE]// flash, noncorrectable error

ECSM_ECC2BIT_IRQ

= ECSM_ECCRNCR_IRQ // ram, noncorrectable error

| ECSM_ECCFNCR_IRQ // flash, noncorrectable error

ECSM_ECC_IRQ

= ECSM_ECC1BIT_IRQ // 1-bit correction

| ECSM_ECC2BIT_IRQ // noncorrectable error

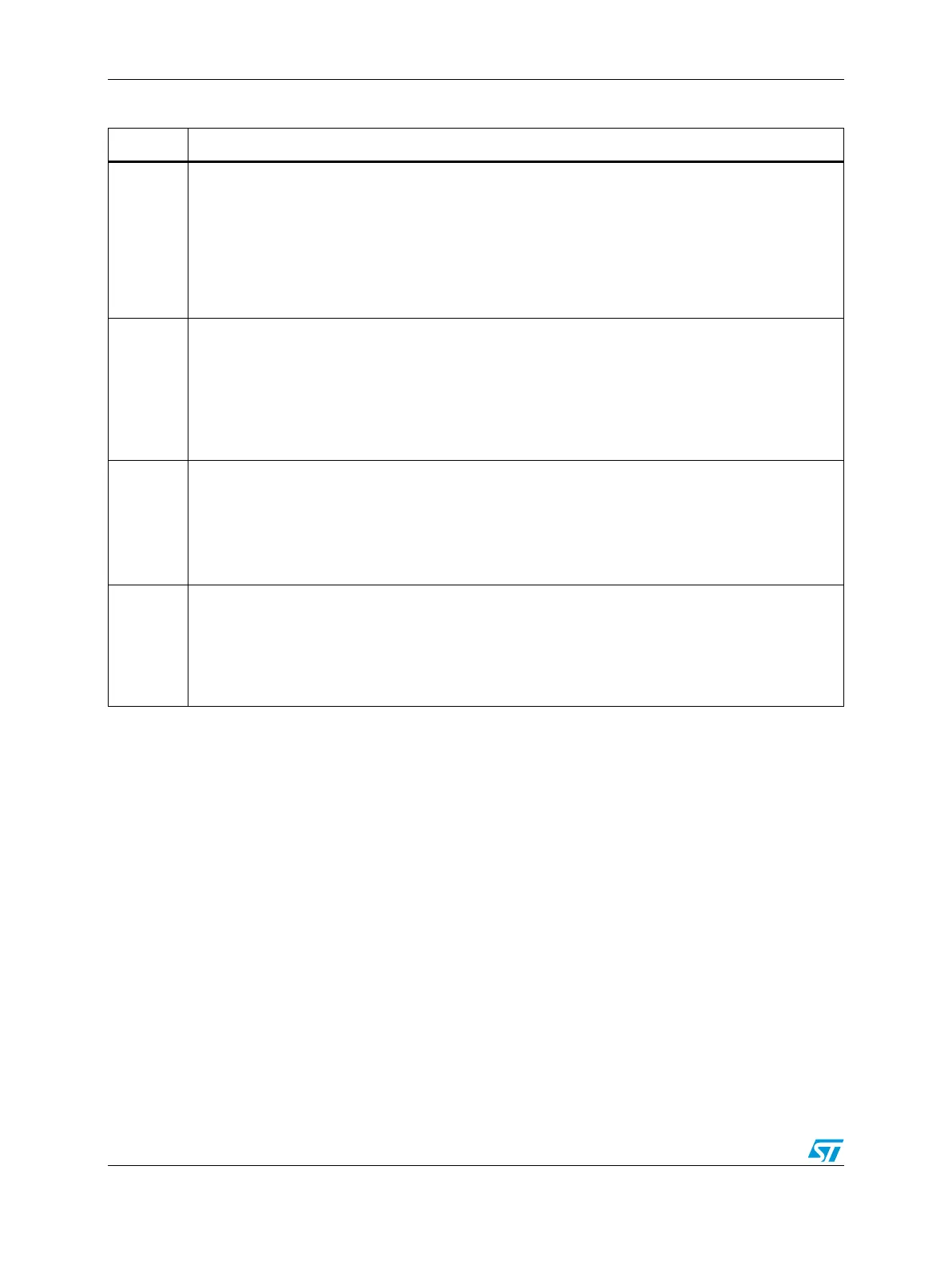

Table 121. ECR field descriptions

Field Description

2

ER1BR

Enable RAM 1-bit Reporting

This bit can only be set if the input enable signal is asserted. This signal is tied to 1 at SoC level and

hence reporting of single-bit memory corrections is always enabled. The occurrence of a single-bit

RAM correction generates a ECSM ECC interrupt request as signaled by the assertion of ESR[R1BC].

The address, attributes and data are also captured in the REAR, RESR, REMR, REAT and REDR

registers.

0 Reporting of single-bit RAM corrections disabled

1 Reporting of single-bit RAM corrections enabled

3

EF1BR

Enable Flash 1-bit Reporting

This bit can only be set if the input enable signal is asserted. This signal is tied to 1 at SoC level and

hence reporting of single-bit memory corrections is always enabled. The occurrence of a single-bit

flash correction generates a ECSM ECC interrupt request as signaled by the assertion of ESR[F1BC].

The address, attributes and data are also captured in the FEAR, FEMR, FEAT and FEDR registers.

0Reporting of single-bit flash corrections disabled

1Reporting of single-bit flash corrections enabled

6

ERNCR

Enable RAM Non-Correctable Reporting

The occurrence of a non-correctable multi-bit RAM error generates a ECSM ECC interrupt request as

signaled by the assertion of ESR[RNCE]. The faulting address, attributes and data are also captured in

the REAR, RESR, REMR, REAT and REDR registers.

0Reporting of non-correctable RAM errors disabled

1Reporting of non-correctable RAM errors enabled

7

EFNCR

Enable Flash Non-Correctable Reporting

The occurrence of a non-correctable multi-bit flash error generates a ECSM ECC interrupt request as

signaled by the assertion of ESR[FNCE]. The faulting address, attributes and data are also captured in

the FEAR, FEMR, FEAT and FEDR registers.

0 Reporting of non-correctable flash errors disabled

1 Reporting of non-correctable flash errors enabled

Loading...

Loading...