RM0046 Mode Entry Module (MC_ME)

Doc ID 16912 Rev 5 169/936

Any modification of the mode configuration register of the currently selected mode will not

be taken into account immediately but on the next request to enter this mode. This means

that transition requests such as RUN0…3 Æ RUN0…3, DRUN Æ DRUN, SAFE Æ SAFE,

and TEST Æ TEST are considered valid mode transition requests. As soon as the mode

request is accepted as valid, the S_MTRANS bit is set till the status in the ME_GS register

matches the configuration programmed in the respective ME_<mode>_MC register.

Note: It is recommended that software poll the S_MTRANS bit in the ME_GS register after

requesting a transition to HALT0 or STOP0 modes.

6.4.2 Modes Details

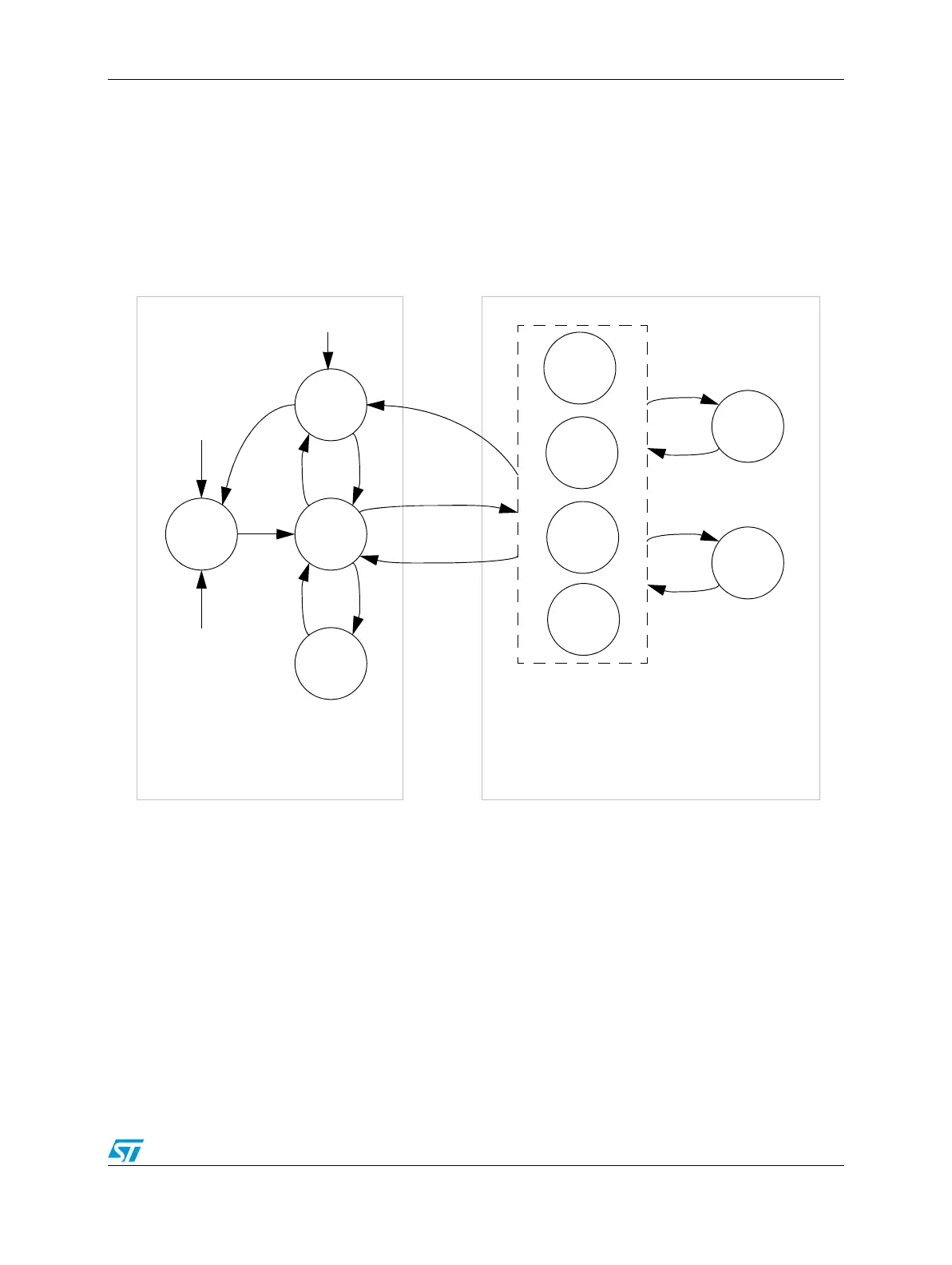

RESET Mode

The device enters this mode on the following events:

● from SAFE, DRUN, RUN0…3, or TEST mode when the TARGET_MODE bit field of the

ME_MCTL register is written with “0000”

● from any mode due to a system reset by the MC_RGM because of some non-

recoverable hardware failure in the system (see the MC_RGM chapter for details)

Transition to this mode is instantaneous, and the system remains in this mode until the reset

sequence is finished. The mode configuration information for this mode is provided by the

SAFE

DRUN

TEST

RESET

RUN0

RUN1

HALT0

STOP0

SYSTEM MODES USER MODES

software

request

non-recoverable

failure

RUN2

RUN3

recoverable

hardware failure

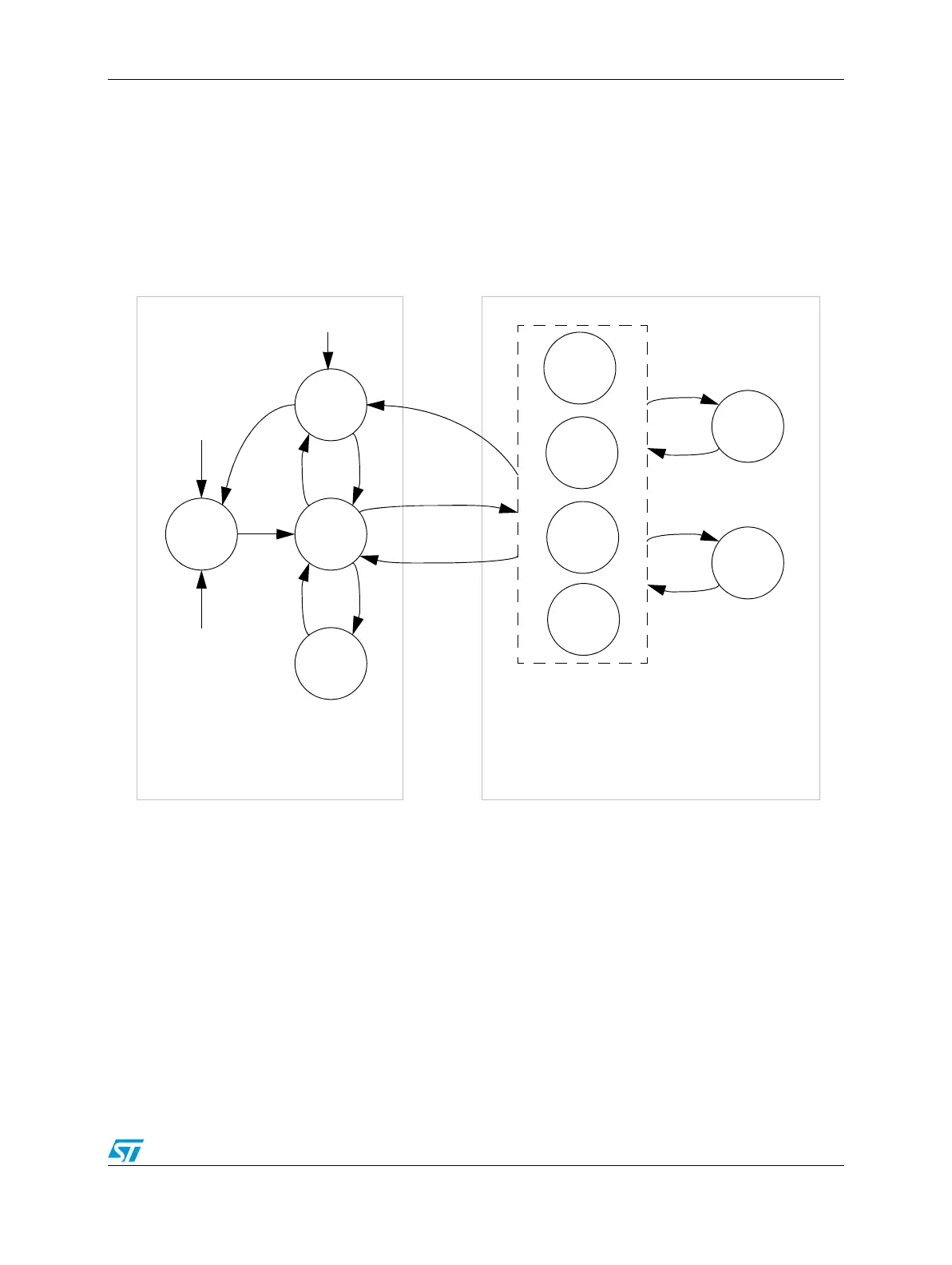

Figure 63. MC_ME Mode Diagram

Loading...

Loading...