RM0046 FlexPWM

Doc ID 16912 Rev 5 697/936

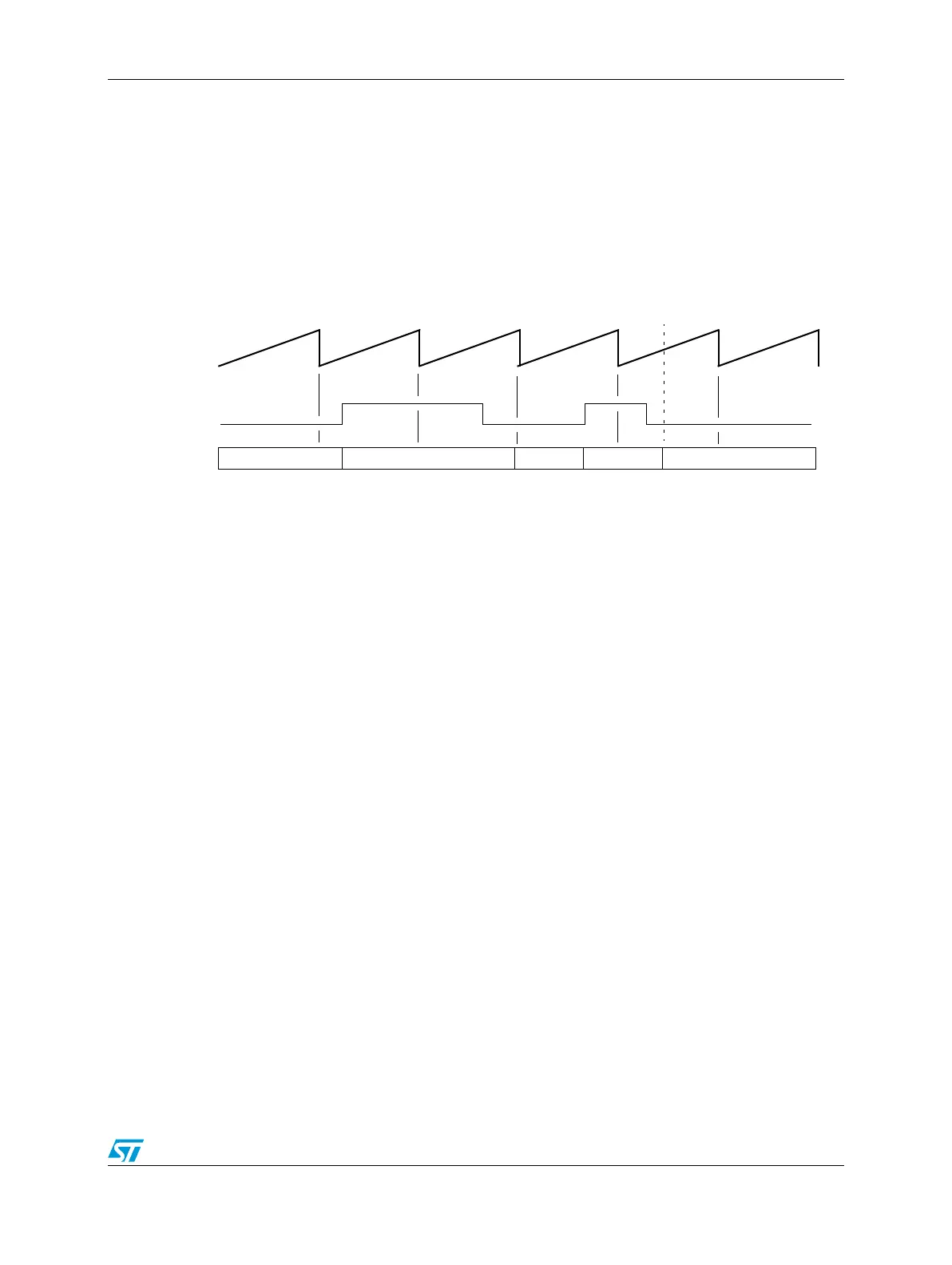

25.8.14 Automatic fault clearing

Setting an automatic clearing mode bit, FAUTOx, configures faults from the FAULTx pin for

automatic clearing.

When FAUTOx is set, disabled PWM pins are enabled when the FAULTx pin returns to logic

one and a new PWM either full or half cycle begins. See Figure 383. Clearing the FFLAGx

flag does not affect disabled PWM pins when FAUTOx is set.

Figure 383. Automatic fault clearing

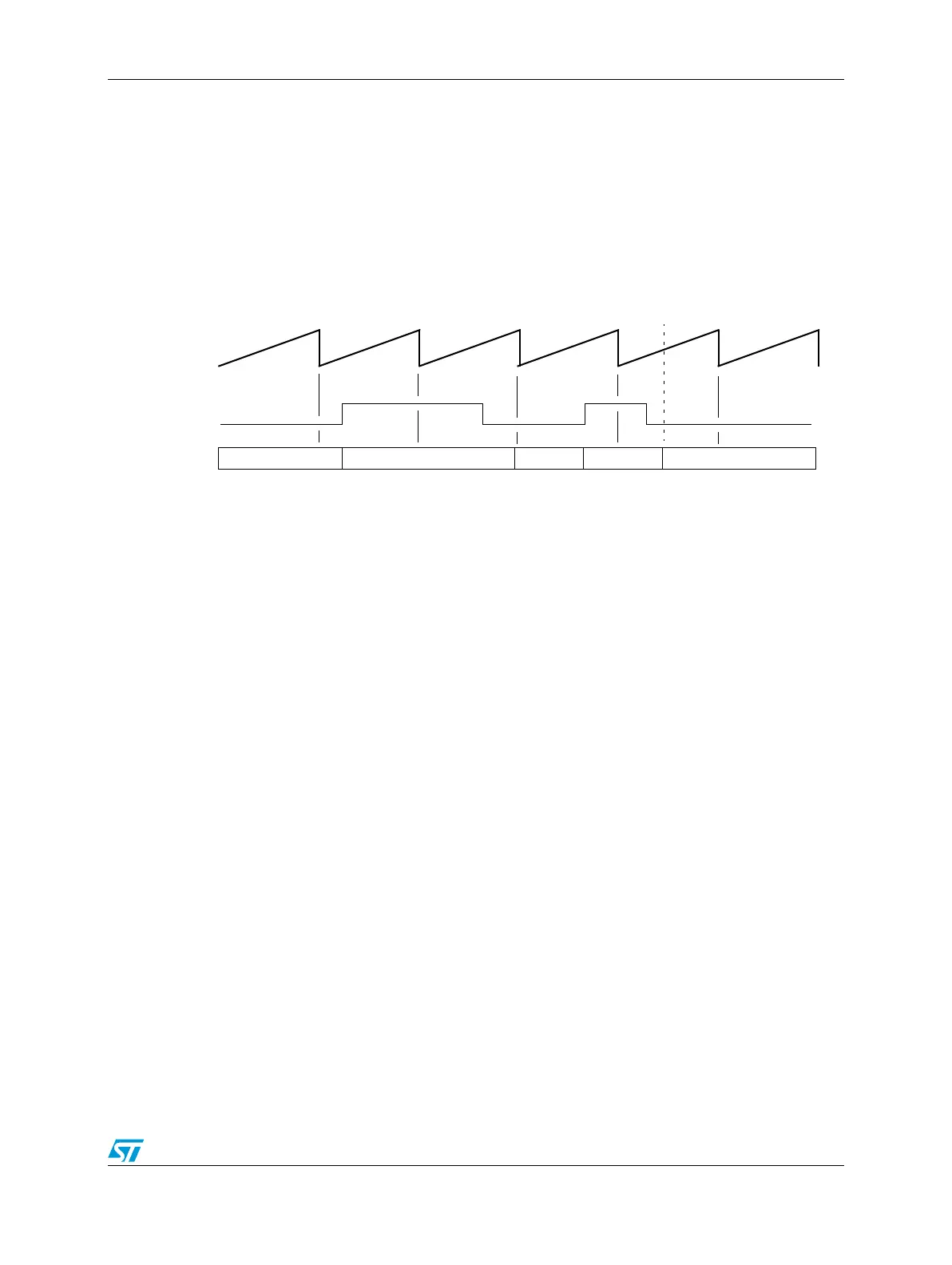

25.8.15 Manual fault clearing

Clearing the automatic clearing mode bit, FAUTOx, configures faults from the FAULTx pin for

manual clearing:

● If the fault safety mode bits, FSAFEx, are clear, then PWM pins disabled by the FAULTx

pins are enabled when:

– Software clears the corresponding FFLAGx flag

– The pins are enabled when the next PWM half cycle begins regardless of the logic

level detected by the filter at the FAULTx pin. See Figure 384.

● If the fault safety mode bits, FSAFEx, are set, then PWM pins disabled by the FAULTx

pins are enabled when:

– Software clears the corresponding FFLAGx flag

– The filter detects a logic one on the FAULTx pin at the start of the next PWM half

cycle boundary. See Figure 385.

FFPINx BIT

COUNT

OUTPUTS

Half

Cycle

ENABLED DISABLED ENABLE DISABLE ENABLED

Loading...

Loading...