RM0046 Fault Collection Unit (FCU)

Doc ID 16912 Rev 5 767/936

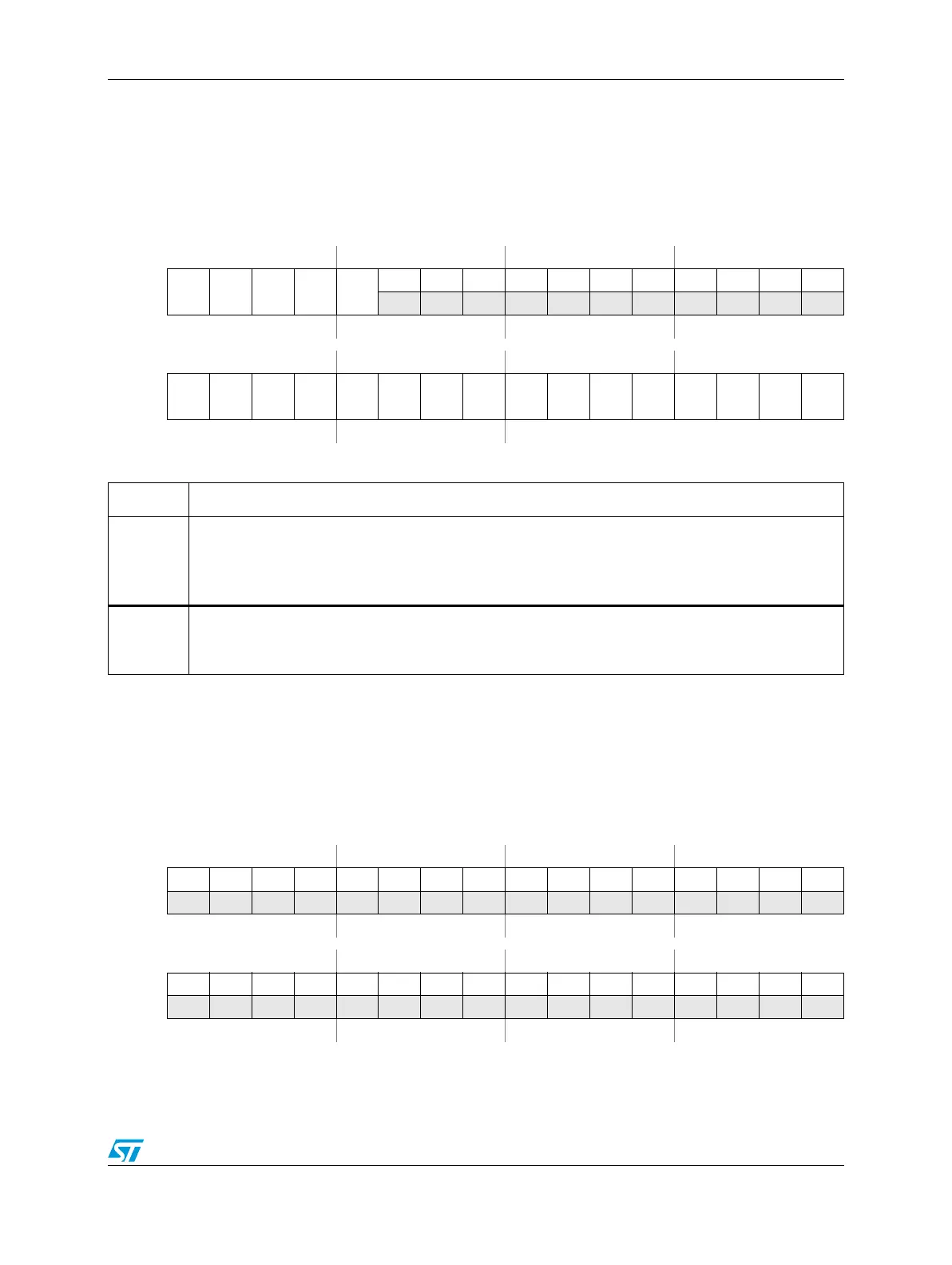

Timeout Enable Register (FCU_TER)

Once a specific fault is enabled, the user can select to move to Alarm or Fault state when a

fault occurs. A timeout enable has no effect if the related fault enable flag is not set.

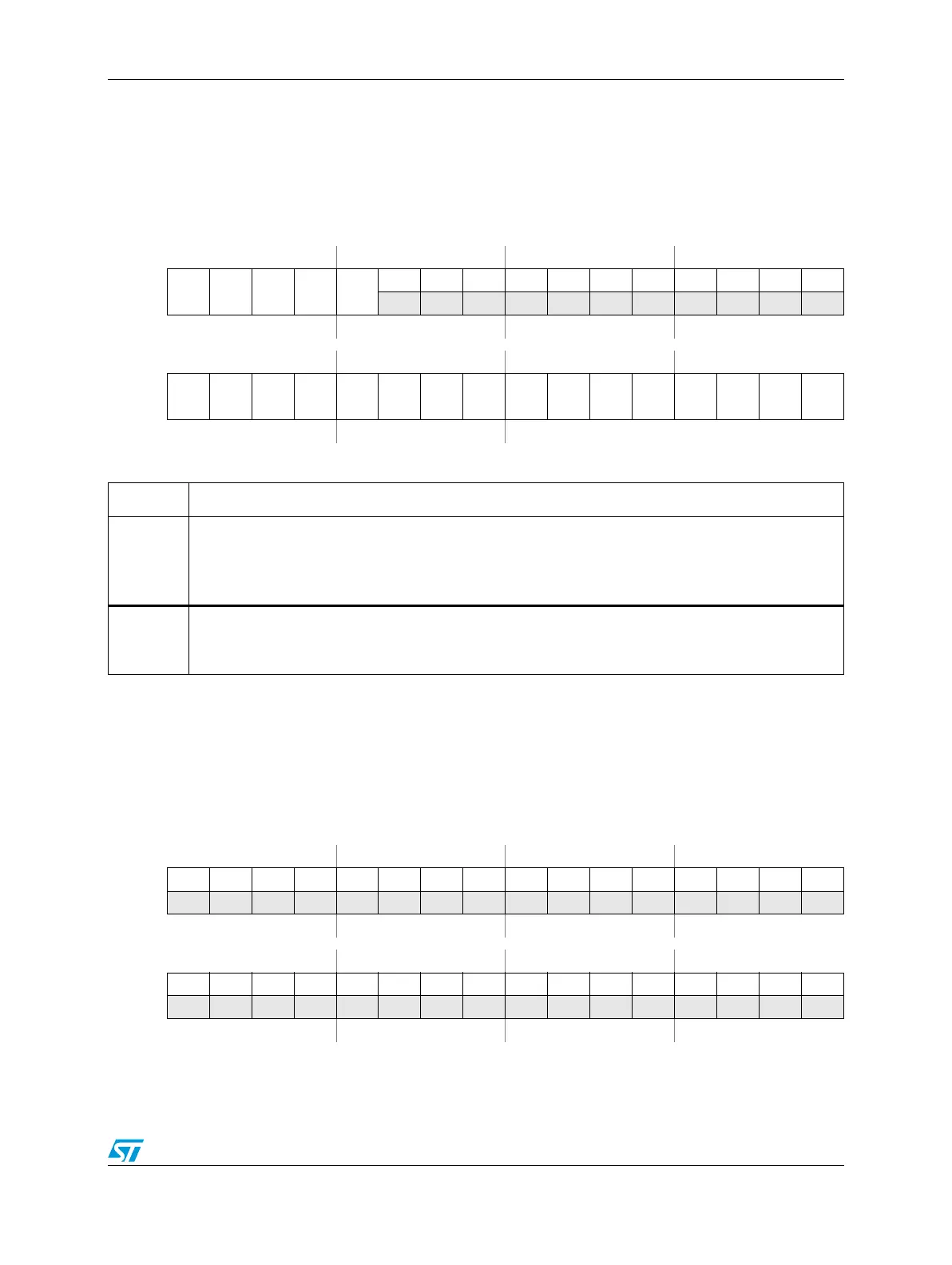

Module State Register (FCU_MSR)

The FCU_MSR indicates the current state of the FCU. Only one of these bits can be set at a

time.

Figure 444. Timeout Enable Register (FCU_TER)

Address:

Base + 0x001C Access: User read/write, Supervisor read/write

0123456789101112131415

R

TESF

0

TESF

1

TESF

2

TESF

3

TESF

4

00000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

TEHF

15

TEHF

14

TEHF

13

TEHF

12

TEHF

11

TEHF

10

TEHF

9

TEHF

8

TEHF

7

TEHF

6

TEHF

5

TEHF

4

TEHF

3

TEHF

2

TEHF

1

TEHF

0

W

Reset0000000000000000

Table 408. FCU_TER field descriptions

Field Description

0:4

TESF0–

TESF4

Timeout Enable for Software Recoverable Fault

0: FCU goes into Fault state on Software recoverable Fault[0:4]

1: FCU goes into Alarm state on Software recoverable Fault[0:4]

Note. TESF1 not implemented or usable on this device

16:31

TEHF15–

TEHF0

Timeout Enable for Hardware Recoverable Fault

0: FCU goes into Fault state on Hardware recoverable Fault[15:0]

1: FCU goes into Alarm state on Hardware recoverable Fault[15:0]

Figure 445. Module State Register (FCU_MSR)

Address:

Base + 0x0020 Access: User read-only, Supervisor read-only

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000 0000S3 S2 S1 S0

W

Reset0000000000000001

Loading...

Loading...